基于USB2.0的高速无线数传接收设备的数据接收存储方法

北京理工大学电子工程系(100081) 李新昌

摘 要:介绍了一种利用USB2.0接口芯片ISP1581并配合FPGA芯片EP1K30TI144和DSP芯片TMS320F206实现无线数传接收设备中数据接收存储的方法。这种方法具有接口简单、使用方便等特点。

关键词:位同步 帧同步 USB2.0 差错控制

数据接收存储技术是信号采集处理领域内的一个重要课题。利用这种技术,可以把信号的实时采集和精确处理在时间上分为两个阶段,有利于获得令人更满意的处理结果。在无线数传接收设备中应用数据接收存储方法时,除了要满足数据传输速率和差错控制方面的要求外,还需要考虑如何使设备易于携带、接口简单、使用方便。

传统外设接口技术不但数据传输速率较低,独占中断、I/O地址、DMA通道等计算机系统关键资源,容易造成资源冲突问题,而且使用时繁杂的安装配置手续也给终端用户带来了诸多不便。近年来,USB接口技术迅速发展,新型计算机纷纷对其提供支持。USB2.0是USB技术发展的最新成果,利用USB2.0接口技术开发计算机外设,不但可以借用其差错控制机制[1][6]减轻开发人员的负担、获得高速数据传输能力(480Mb/s),而且可以实现便捷的机箱外即插即用特性,方便终端用户的使用。

1 无线数传接收设备总体构成

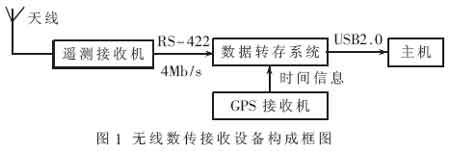

无线数传接收设备是某靶场测量系统的一个重要组成部分。如图1所示,该设备由遥测接收机、GPS接收机和数据转存系统构成。遥测接收机利用天线接收经过调制的无线电波信号,解调后形成传输速率为4Mb/s 的RS-422电平差分串行数据流。以帧同步字打头的有效数据帧周期性地出现在这些串行数据中。数据转存系统从中提取出有效的数据帧,并在帧同步字后插入利用GPS接收机生成的本地时间信息,用于记录该帧数据被接收到的时间,然后送给主机硬盘保存。

在无线数传接收设备中,数据转存系统是实现数据接收存储的关键子系统。下面将详细介绍该系统的硬件实现及工作过程。

2 数据转存系统基本构成及硬件实现

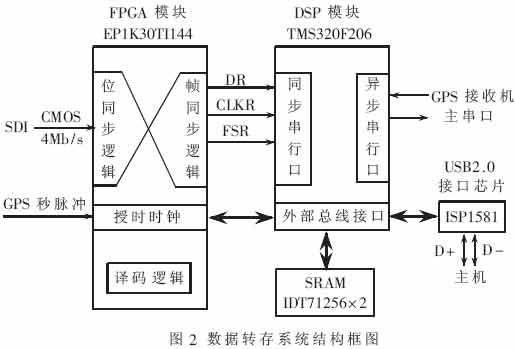

数据转存系统主要由FPGA模块、DSP模块、USB2.0接口芯片构成,各个模块之间的相互关系如图2所示示。图中,4Mb/s的串行数据输入信号SDI已由RS-422差分电平转换为CMOS电平。为突出重点,不太重要的信号连线未在图中绘出。下面分别介绍这几个模块的主要功能。

2.1 FPGA模块实现及其功能

FPGA模块在Altera公司ACEX系列的EP1K30TI144-2芯片中实现。其中主要的功能子模块有:位同步逻辑、帧同步逻辑、授时时钟和译码逻辑。位同步逻辑主要由数字锁相环构成,用于从串行数据输入信号SDI中恢复出位时钟信号。帧同步逻辑从位同步逻辑的输出信号提取帧同步脉冲。两者为DSP利用其同步串行口接收串行数据作好准备。这样,利用一对差分信号线就可以接收同步串行数据,简化了印制电路板的外部接口。授时时钟在DSP和GPS接收机的协助下生成精度为0.1ms的授时信息。译码逻辑用于实现系统互联。

2.2 DSP模块实现及其功能

DSP模块是数据转存系统的主控模块,在TI公司16位定点DSP芯片TMS320F206[4]中实现。在DSP的外部数据空间还配置了32K×16的高速SRAM,可以缓存80余帧数据,用于提高系统的差错控制能力。DSP利用同步串行口接收FPGA送来的同步串行数据,利用异步串行口接收GPS接收机送来时间信息(用于初始化FPGA授时时钟),利用外部总线接口访问FPGA授时时钟、外部SRAM、ISP1581的片内寄存器。可以看出DSP模块主要用于完成数据帧的接收、重组以及转存调度等任务。

2.3 USB2.0接口芯片ISP1581

ISP1581芯片是PHILIPS公司推出的高速USB2.0设备控制器,实现了USB2.0/1.1物理层、协议层,完全符合USB2.0规范,既支持高速(480Mb/s)操作,又支持全速(12Mb/s)操作。ISP1581没有内嵌微处理器,但对微处理器提供了灵活的接口。在上电时,通过配置BUS_CONF/DA0、MODE1、MODE0/DA1引脚电平可以适应绝大多数的微处理器接口类型。例如,通过BUS_CONF/DA0引脚,总线配置可以选择普通处理器模式(Generic Processor mode)或分割总线模式(Split Bus Mode);在普通处理器模式下,通过MODE0/DA1引脚可以选择读写选通为8051风格或者Motorola风格。

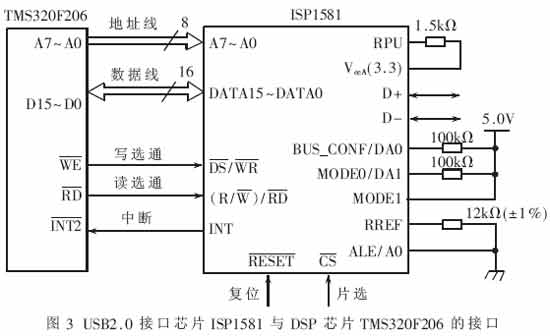

在数据转存系统中,ISP1581用于处理主机的高速数据传输。它工作在普通处理器接口模式下,采用8051风格的读写选通信号,由DSP芯片TMS320F206控制。两者在选定工作方式下的信号连线如图3所示,图中未画出的信号引脚可以悬空,供电引脚的连接方式在参考资料[2]第46页有简明描述。在FPGA译码逻辑的作用下,ISP1581的片内寄存器被映射在DSP的片外数据空间中。DSP通过8位地址线选择要访问的寄存器,在读写选通信号的控制下,利用16位数据线与选定的寄存器交换数据。在访问ISP1581单字节寄存器时,数据总线高字节内容无关紧要。ISP1581通过中断引脚INT向DSP报告发生的总线事件,利用D+、D-引脚完成与主机的数据交换。

USB 相关文章:

- 实现WUSB设备控制器的设计考虑因素(09-12)

- 四种短距离无线监控解决方案的性能对比(09-16)

- Wibree:一个可供选择的新无线联网技术(11-07)

- TI 单芯片手机多媒体电话解决方案(12-01)

- 蓝牙技术硬件实现模式分析(01-11)

- HSDPA:链式发展催生真实的移动宽带(01-12)