基于DSP数字振荡器的移相正弦波发生器设计

时间:11-07

来源:EDN

点击:

0 引 言

产生数字式移相信号的方法有很多。传统的直接数字频率合成(DDS)移相原理是先将正弦波信号数字化,并形成一张数据表存入两片ROM芯片中,此后可通过两片。D/A转换芯片在计数器的控制下连续地循环输出该数据表,就可获得两路正弦波信号。当两片D/A转换芯片所获得的数据序列完全相同时,则转换所得到的两路正弦波信号无相位差。当两片D/A转换芯片所获得的数据序列不同时,则转换所得到的两路正弦波信号就存在着相位差。相位差的值与数据表中数据的总个数及数据地址的偏移量有关。这种处理方式的实质是将数据地址的偏移量映射为信号间的相位值。

数据的偏差可以通过外部微处理器来获得相应的数字量输入,这个数值对应着正弦信号的移相角度。直接频率合成方法具有频率转换时间短、相位噪声性能好、精度高,产生的信号频率范围宽等优点,但由于需要采用地址、相位计算、访问存储器操作等环节,导致直接频率合成器结构复杂、成本高、移相分辨率低。本文利用DSP技术,通过数值迭代方法,即用DSP数字振荡器的实现原理获得两路正弦波信号。通过仿真,硬件实现,能得到设定参数的两路正弦波输出,达到了设计目的,并具有调整方便灵活、分辨率高等特点。数值迭代方法能精确计算角度的正弦值,只需较小的存储空间,选择正弦周期中的样点数、改变样点间的延迟,能产生不同频率的波形,可利用软件改变波形幅度及相位。

1 波形及移相波形发生器的DSP实现原理

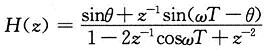

利用DSP通过运算,用叠代的方法产生正弦信号,即数字振荡器。数字振荡器的单位冲击响应为sin(nωT+θ)·u(n)即系统在δ(n)的激励下,产生振荡,输出相位为θ的正弦序列,该系统的系统函数就是冲击响应的Z变换,即

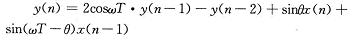

则该系统所对应的差分方程为

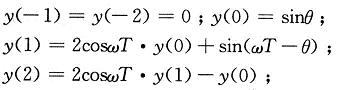

通过叠代可由差分方程求出系统的冲击响应。系统的输入为x(n)=δ(n),初始条件为零。则由差分方程可得:

当n≥3时有:y(n)=2cosωT·y(n-1)-y(n-2)。在n≥3以后,y(n)能用y(n-1)和y(n-2)算出,这是一个递归的差分方程。因此得到如下结论:只要已知系统输出正弦信号角频率ω和采样周期T就可以得到系统差分方程,系统只需每隔T秒时间计算一次差分方程,就可得到当前正弦采样序列y(n)的值。设定的y(1)、y(2)初值不同,初始相位就不同。在设计中,主程序通过键盘输入频率及相位差等数据,在初始化时依输出信号频率、采样速率及相位差等数据先计算出两路正弦信号的初始值y1(1)、y1(2)和y2(1)y2(2),然后开放定时器中断。以后每次进入定时器中断服务程序时,利用前面的y1(1)、y1(2)和y2(1)y2(2),计算出新的y1(0)和y2(0)。虽然两次计算并输出y1(0)和y2(0)有一定的延迟,但由于DSP的高速流水线运行及McBSP高速串行输出,所引起误差将很小。

2 系统硬件实现方案

基于TMS320VC5416 DSP的两路输出移相正弦波的系统结构如图1所示。该系统的中央处理单元采用美国TI(德州仪器)公司的高性能定点数字信号处理芯片TMS320VC5416,TMS 320 VC54.16是TI公司专门针对便携式设备设计的一款低功耗、高性能定点数字信号处理器,同C54系列其它处理器相比运行速度达到160MPIS,片内RAM达到128K,程序可寻址空间达到8M,为大量数据处理提供了丰富条件。特别是VC5416提供了多种片内外设资源;软件可编程等待状态产生器、可编程锁相环时钟产生器、1个16位计时器、6通道直接内存访问控制器(DMA)、3个多通道缓冲串口(McBSP)、8位增强型HPI接口等。

此外,TMS320VC5416支持C和汇编语言混合编程,高效的流水线操作和灵活的寻址方式使其特别适合高速实时信号处理。由于系统有两路正弦信号输出,系统采用两路信号分时传输方式。TLC320AD50C是TI公司出品的一块将A/D和D/A转换功能集成在一起的模拟接口芯片,采用∑-△技术在低系统成本下实现了高精度的A/D和D/A转换。该芯片由一对16 b同步串行转换通道组成,在ADC之后有一个抽取滤波器,在DAC之前有一个插值滤波器。TLC320AD50C支持主从两种工作方式,并且最多支持三个从设备。利用该特点,系统将两片TLC320AD50C串联,使其中一个为主设备另一个为从设备,通过TMS320VC5416的多通道缓冲串口McBSP实现与两片TLC320AD50C间的串行通信。TMS320VC54.16控制两片TLC320AD50C以时分复用方式将数据传送给两片TLC320AD50C进行D/A转换输出。其中AD50C1的M/S接高电平,AD50C2的M/S接低电平,并且利用VC5416的XF引脚为AD50C提供主、次通信选择信号。TLC320AD50被广泛应用于音频数据采集处理中,它可以与TMS320C54xDSP的McBSP无缝串行连接进行数据采集、存储和处理。

SCLK输出时钟,DIN串行输入,DOUT串行输出,FS帧同步信号输出,对应DSP的各相应引脚。MCBSP具有特点:①串口的接收,发送时钟既可由外部设备提供,又可由内部时钟发生器提供;②帧同步信号和数据时钟信号的极性可编程,内部时钟和帧信号发生器也可由软件编程控制;③串口的信号发送和接收部分既可单独运行,又可以在一起配合工作;④CPU的中断信号和DMA的同步信号使得McBSP串口可由CPU控制运行,还可脱离CPU通过DMA直接存取内存单独运行;⑤多通道选择部分使得串口具备了多通道信号的通信能力,他的多通道接收和发送能力可达128个信道;⑥数据宽度可在8b、12b、16b、20b、24b、32b中任意选择,并可对数据进行A律和U律压缩和扩展。McBSP串口包括一个数据通道和一个控制通道,数据通道完成数据的发送和接收。McBSP通过DX引脚发送数据、DR引脚接收数据。控制通道完成的任务包括内部时钟的产生、帧同步信号的产生、对这些信号的控制以及多通路的选择等。控制通道还负责产生中断信号送往CPU,产生同步事件信号通知DMA控制器。控制信息则是通过控制通道以时钟和帧同步信号的形式传送。

产生数字式移相信号的方法有很多。传统的直接数字频率合成(DDS)移相原理是先将正弦波信号数字化,并形成一张数据表存入两片ROM芯片中,此后可通过两片。D/A转换芯片在计数器的控制下连续地循环输出该数据表,就可获得两路正弦波信号。当两片D/A转换芯片所获得的数据序列完全相同时,则转换所得到的两路正弦波信号无相位差。当两片D/A转换芯片所获得的数据序列不同时,则转换所得到的两路正弦波信号就存在着相位差。相位差的值与数据表中数据的总个数及数据地址的偏移量有关。这种处理方式的实质是将数据地址的偏移量映射为信号间的相位值。

数据的偏差可以通过外部微处理器来获得相应的数字量输入,这个数值对应着正弦信号的移相角度。直接频率合成方法具有频率转换时间短、相位噪声性能好、精度高,产生的信号频率范围宽等优点,但由于需要采用地址、相位计算、访问存储器操作等环节,导致直接频率合成器结构复杂、成本高、移相分辨率低。本文利用DSP技术,通过数值迭代方法,即用DSP数字振荡器的实现原理获得两路正弦波信号。通过仿真,硬件实现,能得到设定参数的两路正弦波输出,达到了设计目的,并具有调整方便灵活、分辨率高等特点。数值迭代方法能精确计算角度的正弦值,只需较小的存储空间,选择正弦周期中的样点数、改变样点间的延迟,能产生不同频率的波形,可利用软件改变波形幅度及相位。

1 波形及移相波形发生器的DSP实现原理

利用DSP通过运算,用叠代的方法产生正弦信号,即数字振荡器。数字振荡器的单位冲击响应为sin(nωT+θ)·u(n)即系统在δ(n)的激励下,产生振荡,输出相位为θ的正弦序列,该系统的系统函数就是冲击响应的Z变换,即

|

|

通过叠代可由差分方程求出系统的冲击响应。系统的输入为x(n)=δ(n),初始条件为零。则由差分方程可得:

|

当n≥3时有:y(n)=2cosωT·y(n-1)-y(n-2)。在n≥3以后,y(n)能用y(n-1)和y(n-2)算出,这是一个递归的差分方程。因此得到如下结论:只要已知系统输出正弦信号角频率ω和采样周期T就可以得到系统差分方程,系统只需每隔T秒时间计算一次差分方程,就可得到当前正弦采样序列y(n)的值。设定的y(1)、y(2)初值不同,初始相位就不同。在设计中,主程序通过键盘输入频率及相位差等数据,在初始化时依输出信号频率、采样速率及相位差等数据先计算出两路正弦信号的初始值y1(1)、y1(2)和y2(1)y2(2),然后开放定时器中断。以后每次进入定时器中断服务程序时,利用前面的y1(1)、y1(2)和y2(1)y2(2),计算出新的y1(0)和y2(0)。虽然两次计算并输出y1(0)和y2(0)有一定的延迟,但由于DSP的高速流水线运行及McBSP高速串行输出,所引起误差将很小。

2 系统硬件实现方案

基于TMS320VC5416 DSP的两路输出移相正弦波的系统结构如图1所示。该系统的中央处理单元采用美国TI(德州仪器)公司的高性能定点数字信号处理芯片TMS320VC5416,TMS 320 VC54.16是TI公司专门针对便携式设备设计的一款低功耗、高性能定点数字信号处理器,同C54系列其它处理器相比运行速度达到160MPIS,片内RAM达到128K,程序可寻址空间达到8M,为大量数据处理提供了丰富条件。特别是VC5416提供了多种片内外设资源;软件可编程等待状态产生器、可编程锁相环时钟产生器、1个16位计时器、6通道直接内存访问控制器(DMA)、3个多通道缓冲串口(McBSP)、8位增强型HPI接口等。

此外,TMS320VC5416支持C和汇编语言混合编程,高效的流水线操作和灵活的寻址方式使其特别适合高速实时信号处理。由于系统有两路正弦信号输出,系统采用两路信号分时传输方式。TLC320AD50C是TI公司出品的一块将A/D和D/A转换功能集成在一起的模拟接口芯片,采用∑-△技术在低系统成本下实现了高精度的A/D和D/A转换。该芯片由一对16 b同步串行转换通道组成,在ADC之后有一个抽取滤波器,在DAC之前有一个插值滤波器。TLC320AD50C支持主从两种工作方式,并且最多支持三个从设备。利用该特点,系统将两片TLC320AD50C串联,使其中一个为主设备另一个为从设备,通过TMS320VC5416的多通道缓冲串口McBSP实现与两片TLC320AD50C间的串行通信。TMS320VC54.16控制两片TLC320AD50C以时分复用方式将数据传送给两片TLC320AD50C进行D/A转换输出。其中AD50C1的M/S接高电平,AD50C2的M/S接低电平,并且利用VC5416的XF引脚为AD50C提供主、次通信选择信号。TLC320AD50被广泛应用于音频数据采集处理中,它可以与TMS320C54xDSP的McBSP无缝串行连接进行数据采集、存储和处理。

SCLK输出时钟,DIN串行输入,DOUT串行输出,FS帧同步信号输出,对应DSP的各相应引脚。MCBSP具有特点:①串口的接收,发送时钟既可由外部设备提供,又可由内部时钟发生器提供;②帧同步信号和数据时钟信号的极性可编程,内部时钟和帧信号发生器也可由软件编程控制;③串口的信号发送和接收部分既可单独运行,又可以在一起配合工作;④CPU的中断信号和DMA的同步信号使得McBSP串口可由CPU控制运行,还可脱离CPU通过DMA直接存取内存单独运行;⑤多通道选择部分使得串口具备了多通道信号的通信能力,他的多通道接收和发送能力可达128个信道;⑥数据宽度可在8b、12b、16b、20b、24b、32b中任意选择,并可对数据进行A律和U律压缩和扩展。McBSP串口包括一个数据通道和一个控制通道,数据通道完成数据的发送和接收。McBSP通过DX引脚发送数据、DR引脚接收数据。控制通道完成的任务包括内部时钟的产生、帧同步信号的产生、对这些信号的控制以及多通路的选择等。控制通道还负责产生中断信号送往CPU,产生同步事件信号通知DMA控制器。控制信息则是通过控制通道以时钟和帧同步信号的形式传送。

- 基于IXP421的VoIP网关及其性能测评(10-02)

- 新一代移动通信系统的关键技术(10-26)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 设计基于TMS320LF2407的低功耗中文人机界面 (04-16)

- USB接口芯片的原理及应用 (04-15)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)