STM32FSMC机制FlaSh存储器扩展

时间:10-29

来源:EDN

点击:

(3)配置存储器时序参数

FSMC通过使用可编程的存储器时序参数寄存器,拓宽了可选用的外部存储器的速度范围。FSMC的NORFlash控制器支持同步和异步突发两种访问方式。选用同步突发访问方式时,FSMC将HCLK(系统时钟)分频后,发送给外部存储器作为同步时钟信号FSMC_CLK。此时需要的设置的时间参数有2个:

①HCLK与FSMC_CLK的分频系数(CLKdiv),可以为2~16分频;

②同步突发访问中获得第1个数据所需要的等待延迟(DATLAT)。

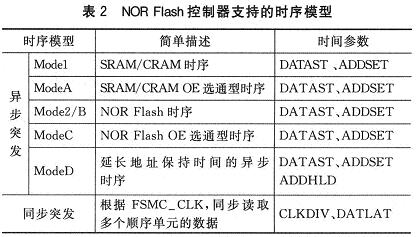

对于异步突发访问方式,FSMC主要设置3个时间参数:地址建立时间(ADDSET)、数据建立时间(DATAST)和地址保持时间(ADDHLD)。FSMC综合了SRAM/ROM、PSRAM和NOR Flash产品的信号特点,定义了4种不同的异步时序模型。选用不同的时序模型时,需要设置不同的时序参数,如表2所列。在实际扩展时,根据选用存储器的特征确定时序模型,从而确定各时间参数与存储器读/写周期参数指标之间的计算关系;利用该计算关系和存储芯片数据手册中给定的参数指标,可计算出FSMC所需要的各时间参数,从而对时间参数寄存器进行合理的配置。

3 STM2扩展S29GL系列NOR Flash实例

3.1 S29GL系列NOR Flash简介

Spansion公司的S29GL系列芯片是采用90nm技术制造的高集成度NOR Flash存储芯片,提供16~128 MB可选容量,支持最快25 ns的页访问速度和11O ns的随机访问速度,带有最大64字节的写缓冲区,以提供更快、更高效的编程,是嵌入式系统设计中大容量存储器扩展的理想选择。本文选用的型号为S29GL512P,容量为512×64K字(总容量64 MB),扩展到NOR Flash控制器管理的BANK1的第2个子BANK。

3.2 STM32与S29GL512P的电路连接

S25GL512P可通过控制引脚BYTE选择对芯片的访问单位(字/字节),区别在于:

①对于芯片引脚DQ15,字模式时传送最高数据位D15;字节模式时传送最低地址A-1。

②字模式时,数据引脚D0~D15上传送数据信号;字节模式时,只有D0~D7上有信号。

此处,将BYTE上拉到高电平,选择16位的字访问单位。FSMC数据线FSMC_D[15:0]与S29GL512P的D15~D0对应连接;FSMC地址线FSMC_A[25:0]的低25根与S29GL512P的地址线A[24:0]对应连接。

由于S29GL512P芯片映射到BANK1的子BANK2,可确定其片选线应连接FSMC片选控制线FSMC_NE2。S29GL512P的RY/BY引脚连接FSMC的FSMC_NWAIT引脚,提供等待信号。

3.3 FSMC的配置

根据S29GL512P的映射位置,需要对FSMC_BCR2和FSMC_BTR2/BWTR2寄存器进行配置。

(1)FSMC_BCR2

配置S29GL512P的读/写采用统一时间参数,只需要设置时间寄存器FSMC_BTR2。配置存储器类型为NORFlash,数据总线宽度为16位(字),不采用地址/数据复用,使能BANK1的子BANK2。

(2)FSMC_BTR2

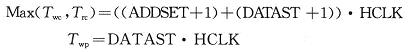

由表2可知,异步NOR Flash时序模型Mode2/B需要设置时间参数DATAST和ADDSET。根据时序图,两个参数的计算公式如下:

式中:Twc和Trc为所选存储芯片的写周期长度和读操作周期长度;Twp为所选存储芯片的写信号持续长度。根据S29GL512P用户手册,可知参数Twc=Trc=130 ns,Twp=35 ns。设STM32微控制器采用72 MHz主频,则HCLK=(1/72×10-6)s。通过上述公式计算,可取值为:DATAST=2,ADDSET=5。

为了达到更好的控制效果,还应考虑FSMC自身延迟问题,使用校正公式:

式中:TAVQV为所选存储芯片访问过程中,从地址有效至数据有效的时间域;Tsu(Data_NE)为STM32特征参数,从数据有效到FSMC_NE(片选)失效时间域;Ttv(A_NE)为STM32特征参数,从FSMC_NE有效至地址有效的时间域。

TAVQV=130 ns,Tsu(Data_NE)+Ttv(A_NE]=36 ns,对DATAST参数进行校正,可得DATAST=3。

3.4 应用STM32固件对FSMC进行初始化配置

ST公司为用户开发提供了完整、高效的工具和固件库,其中使用C语言编写的固件库提供了覆盖所有标准外设的函数,使用户无需使用汇编操作外设特性,从而提高了程序的可读性和易维护性。

STM32固件库中提供的FSMC的NOR Flash控制器操作固件,主要包括2个数据结构和3个函数。数据结构FSMC_NORSRAMTimingInitTypeDef对应时间参数寄存器FSMC_BTR和FSMC_BWTR的结构定义;

FSMC_NORSRAMinitTypeDef对应特征配置寄存器FSMC_BCR的结构定义,并包含2个指向对应BANK的FSMC_BTR和FSMC_BWTR寄存器的FSMC_NORSRAMTimingInitTypeDef结构指针。针对上述S29GL512P芯片扩展要求,利用固件库进行的主要初始化操作如下:

结 语

STM32作为新一代ARM Cortex-M3核处理器,其卓越的性能和功耗控制能够适用于广泛的应用领域;而其特殊的可变静态存储技术FSMC具有高度的灵活性,对于存储容量要求较高的嵌入式系统设计,能够在不增加外部分立器件的情况下,扩展多种不同类型和容量的存储芯片,降低了系统设计的复杂性,提高了系统的可靠性。

编辑:博子

FSMC通过使用可编程的存储器时序参数寄存器,拓宽了可选用的外部存储器的速度范围。FSMC的NORFlash控制器支持同步和异步突发两种访问方式。选用同步突发访问方式时,FSMC将HCLK(系统时钟)分频后,发送给外部存储器作为同步时钟信号FSMC_CLK。此时需要的设置的时间参数有2个:

①HCLK与FSMC_CLK的分频系数(CLKdiv),可以为2~16分频;

②同步突发访问中获得第1个数据所需要的等待延迟(DATLAT)。

对于异步突发访问方式,FSMC主要设置3个时间参数:地址建立时间(ADDSET)、数据建立时间(DATAST)和地址保持时间(ADDHLD)。FSMC综合了SRAM/ROM、PSRAM和NOR Flash产品的信号特点,定义了4种不同的异步时序模型。选用不同的时序模型时,需要设置不同的时序参数,如表2所列。在实际扩展时,根据选用存储器的特征确定时序模型,从而确定各时间参数与存储器读/写周期参数指标之间的计算关系;利用该计算关系和存储芯片数据手册中给定的参数指标,可计算出FSMC所需要的各时间参数,从而对时间参数寄存器进行合理的配置。

|

3.1 S29GL系列NOR Flash简介

Spansion公司的S29GL系列芯片是采用90nm技术制造的高集成度NOR Flash存储芯片,提供16~128 MB可选容量,支持最快25 ns的页访问速度和11O ns的随机访问速度,带有最大64字节的写缓冲区,以提供更快、更高效的编程,是嵌入式系统设计中大容量存储器扩展的理想选择。本文选用的型号为S29GL512P,容量为512×64K字(总容量64 MB),扩展到NOR Flash控制器管理的BANK1的第2个子BANK。

3.2 STM32与S29GL512P的电路连接

S25GL512P可通过控制引脚BYTE选择对芯片的访问单位(字/字节),区别在于:

①对于芯片引脚DQ15,字模式时传送最高数据位D15;字节模式时传送最低地址A-1。

②字模式时,数据引脚D0~D15上传送数据信号;字节模式时,只有D0~D7上有信号。

此处,将BYTE上拉到高电平,选择16位的字访问单位。FSMC数据线FSMC_D[15:0]与S29GL512P的D15~D0对应连接;FSMC地址线FSMC_A[25:0]的低25根与S29GL512P的地址线A[24:0]对应连接。

由于S29GL512P芯片映射到BANK1的子BANK2,可确定其片选线应连接FSMC片选控制线FSMC_NE2。S29GL512P的RY/BY引脚连接FSMC的FSMC_NWAIT引脚,提供等待信号。

3.3 FSMC的配置

根据S29GL512P的映射位置,需要对FSMC_BCR2和FSMC_BTR2/BWTR2寄存器进行配置。

(1)FSMC_BCR2

配置S29GL512P的读/写采用统一时间参数,只需要设置时间寄存器FSMC_BTR2。配置存储器类型为NORFlash,数据总线宽度为16位(字),不采用地址/数据复用,使能BANK1的子BANK2。

(2)FSMC_BTR2

由表2可知,异步NOR Flash时序模型Mode2/B需要设置时间参数DATAST和ADDSET。根据时序图,两个参数的计算公式如下:

|

为了达到更好的控制效果,还应考虑FSMC自身延迟问题,使用校正公式:

|

TAVQV=130 ns,Tsu(Data_NE)+Ttv(A_NE]=36 ns,对DATAST参数进行校正,可得DATAST=3。

3.4 应用STM32固件对FSMC进行初始化配置

ST公司为用户开发提供了完整、高效的工具和固件库,其中使用C语言编写的固件库提供了覆盖所有标准外设的函数,使用户无需使用汇编操作外设特性,从而提高了程序的可读性和易维护性。

STM32固件库中提供的FSMC的NOR Flash控制器操作固件,主要包括2个数据结构和3个函数。数据结构FSMC_NORSRAMTimingInitTypeDef对应时间参数寄存器FSMC_BTR和FSMC_BWTR的结构定义;

FSMC_NORSRAMinitTypeDef对应特征配置寄存器FSMC_BCR的结构定义,并包含2个指向对应BANK的FSMC_BTR和FSMC_BWTR寄存器的FSMC_NORSRAMTimingInitTypeDef结构指针。针对上述S29GL512P芯片扩展要求,利用固件库进行的主要初始化操作如下:

|

STM32作为新一代ARM Cortex-M3核处理器,其卓越的性能和功耗控制能够适用于广泛的应用领域;而其特殊的可变静态存储技术FSMC具有高度的灵活性,对于存储容量要求较高的嵌入式系统设计,能够在不增加外部分立器件的情况下,扩展多种不同类型和容量的存储芯片,降低了系统设计的复杂性,提高了系统的可靠性。

编辑:博子

- ST发布32位微控制器/系统级芯片STM32W 助力无线监视应用(09-15)

- SIM32F107VCT6平台的bxCAN标识符过滤技术与应用(10-12)

- 基于IDP卫星通信模块的远洋船舶实时监控系统(03-16)

- 基于电磁耦合的水下无线能量传输系统(11-24)

- 轻松设计ZIGBEE应用系统(12-10)

- 基于Cortex-M3的嵌入式以太网门禁系统设计(12-16)