基于DSP的USB数据传输系统设计

时间:10-26

来源:EDN

点击:

引 言

由于DSP芯片的不断发展,以及它处理数据速度快、处理数据量大的优势,已经广泛应用到数字信号处理的许多领域。在CT图像重建系统中,DSP处理的数据需要上传到PC机进行存储、显示或进行数据分析等,这就产生了PC机和DSP的数据传输问题。USB总线具有传输速度高,以及即插即用等特点,得到越来越广泛的应用,利用USB总线实现DSP和PC机的通信,从而解决图像信号的实时传输问题。Cypress公司生产的CY7C68001通用USB 2.0接口控制器是基于应用层编程的接口器件,使用简单,开发方便。

在此,以TMS320C6416为例,讨论如何使用CY7C68001对TMS32OC6416进行USB接口设计,实现DSP和PC机通信,将DSP处理过的图像信号实时传到计算机中。

1 DSP与USB接口的硬件设计

TMS320C6416是TI的高性能32位定点DSP,内核采用超长指令字(VLIW)体系结构,有8个功能单元、64个32 b通用寄存器。一个时钟周期同时执行8条指令,主频可达1 GHz,处理性能高达8 000 MIPS,支持8/16/32/64 b的数据类型。

CY7C68001用来连接微处理器或DSP的DMA从装置,内部不含微处理器;支持高速(480 Mb/s)或全速(12 Mb/s)USB数据传输;提供USB 2.0协议要求的全部4种传输方式(控制传输、中断传输、批量传输和同步传输),可以满足用户对各种类型数据传输的需求。

1.1 接口的硬件设计

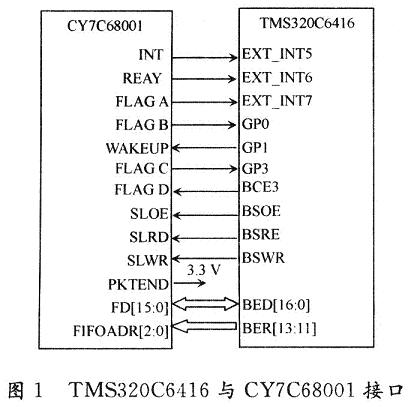

在该设计方案中,CY7C68001通过EMIFB与TMS320C6416进行异步通信,各个引脚的连接如图1所示。DSP控制CY7C68001完成DSP与PC之间的异步通信。CY7C68001的相关引脚在接口中的作用:INT:表明CY7C68001有数据将要被读出,或者有中断事件发生;READY:通知TMS320C6416可以对CY7C68001进行读写;FLAGA,FLAGB,FLAGC:反应由FAIFOADR[2:0]选择的FIFO的状态;FLAGD:为片选信号;SLOE为CY7C68001驱动数据总线;SLRD:并口读有效信号,在SLRD有效且同步通信时,FIFO指针在每个IFCLK的上升沿递增;PKTEND:总是高电平,将当前的缓冲区提交给USB;FD[15:0]:数据总线;FIFO[2:0]:提供与TMS320C6416接口的FIFO地址选择。

1.2 接口的访问

CY7C68001提供给DSP两种软件接口:

(1)命令接口:用来访问CY7C68001寄存器、End-point0缓冲器及描述表;

(2)FIFO数据接口:用来访问4个1 KB的FIFO中的数据。通过编程直接作为FIFO分配给。EP2,EP4,EP6,EP8。这两个外部接口均可以通过同步或异步方式进行访问。在此均采用异步的方式进行访问,命令口的命令字如下:

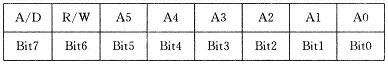

在表1中,A/D用于地址/数据的选择,当其为0时,表示本操作为数据读或写;当其为1时,表示本操作为地址写。R/W用于读/写操作的选择,当其为0时,进行写,当其为1时,进行读。A[5:0]用于地址/数据的选择,当Bit7=0时,D[3:0]为数据半字节;D[5:4]为未用,命令字为8位,故命令字数据分二次读出或写入;当Bit7=1时,D[5:0]包含将要寻址的命令寄存器地址。

2 USB软件设计

USB的软件设计包括三方面:固件设计、驱动程序设计和主机端应用程序设计。

2.1 固件设计

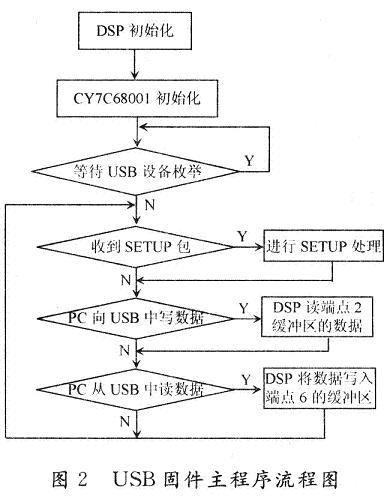

所有基于微控制器及外围电路功能设备的正常工作都离不开固件的参与,固件的作用就是辅助硬件工作。没有固件的参与和控制,硬件设备无法实现预期的功能。USB设备也不例外,必须编写固件程序来辅助硬件完成USB的通信任务。由于采用不带MCU内核的USB接口芯片,USB的应用层协议应该通过对TMS320C6416的编程来实现,USB固件的加载必须靠DSP的控制CY7C68001来完成。在CCS中用C语言完成固件程序的编写,程序流程图如图2所示。

根据程序流程图,固件设计思路如下:

(1)初始化工作。包括设置一些特殊功能寄存器的初值,以实现所需的设备属性或功能,例如:配置端口、使能端点、开中断。该设计中,使CY7C68001工作于异步FIFO模式,将4 KB的FIFO对应到两个端点(Endpoint),即Endpoint2和Endpoint6。

(2)辅助硬件完成设备的重新列举过程。包括模拟设备的断开与重新连接,对接收到的设置包进行分析判断,从而对主机的设备请求做出适当的响应,完成主机对设备的配置任务。

(3)对中断的处理。CY7C68001有6个中断源,可以分别通过中断使能对寄存器的各位进行设置。一旦中断事件发生,CY7C68001的INT引脚就被置低,并且置中断使能寄存器的相应位(即中断使能寄存器同时充当中断标志寄存器,中断使能寄存器具有读写属性)。当中断发生时,中断标志寄存器的状态字映射到FD[7:0];中断发生后。DSP对CY7C68001简单的一次读操作即可获取中断信息,识别中断源并进行相应处理。相对于中断标志寄存器的读操作,其他对CY7C68001寄存器的读操作通常要先发送一次请求,并且收到READY响应后.才可以读取数据。

(4)数据的接收与发送。在读数据时,应首先判断CY7C68001的FIFO2是否为空,如果不为空,才将数据读进来。在写数据时,还要判断要写的数据个数是否为512 B的整倍数,如果不是,则使用PKTEND信号来标识数据包的结束。EP2和EP6分别对应存放USB需要上传与接收的数据。其中,EP2为OUT型,负责从主机接收数据;EP6为IN型,负责向主机发送数据。EP2和EP6均采用批量(BULK)传输方式,这种传输方式具有数据可靠,传输速率高等特点,特别适合大批量数据传输。部分关键代码如下:

DSP读端点2中的数据:

由于DSP芯片的不断发展,以及它处理数据速度快、处理数据量大的优势,已经广泛应用到数字信号处理的许多领域。在CT图像重建系统中,DSP处理的数据需要上传到PC机进行存储、显示或进行数据分析等,这就产生了PC机和DSP的数据传输问题。USB总线具有传输速度高,以及即插即用等特点,得到越来越广泛的应用,利用USB总线实现DSP和PC机的通信,从而解决图像信号的实时传输问题。Cypress公司生产的CY7C68001通用USB 2.0接口控制器是基于应用层编程的接口器件,使用简单,开发方便。

在此,以TMS320C6416为例,讨论如何使用CY7C68001对TMS32OC6416进行USB接口设计,实现DSP和PC机通信,将DSP处理过的图像信号实时传到计算机中。

1 DSP与USB接口的硬件设计

TMS320C6416是TI的高性能32位定点DSP,内核采用超长指令字(VLIW)体系结构,有8个功能单元、64个32 b通用寄存器。一个时钟周期同时执行8条指令,主频可达1 GHz,处理性能高达8 000 MIPS,支持8/16/32/64 b的数据类型。

CY7C68001用来连接微处理器或DSP的DMA从装置,内部不含微处理器;支持高速(480 Mb/s)或全速(12 Mb/s)USB数据传输;提供USB 2.0协议要求的全部4种传输方式(控制传输、中断传输、批量传输和同步传输),可以满足用户对各种类型数据传输的需求。

1.1 接口的硬件设计

在该设计方案中,CY7C68001通过EMIFB与TMS320C6416进行异步通信,各个引脚的连接如图1所示。DSP控制CY7C68001完成DSP与PC之间的异步通信。CY7C68001的相关引脚在接口中的作用:INT:表明CY7C68001有数据将要被读出,或者有中断事件发生;READY:通知TMS320C6416可以对CY7C68001进行读写;FLAGA,FLAGB,FLAGC:反应由FAIFOADR[2:0]选择的FIFO的状态;FLAGD:为片选信号;SLOE为CY7C68001驱动数据总线;SLRD:并口读有效信号,在SLRD有效且同步通信时,FIFO指针在每个IFCLK的上升沿递增;PKTEND:总是高电平,将当前的缓冲区提交给USB;FD[15:0]:数据总线;FIFO[2:0]:提供与TMS320C6416接口的FIFO地址选择。

|

1.2 接口的访问

CY7C68001提供给DSP两种软件接口:

(1)命令接口:用来访问CY7C68001寄存器、End-point0缓冲器及描述表;

(2)FIFO数据接口:用来访问4个1 KB的FIFO中的数据。通过编程直接作为FIFO分配给。EP2,EP4,EP6,EP8。这两个外部接口均可以通过同步或异步方式进行访问。在此均采用异步的方式进行访问,命令口的命令字如下:

|

在表1中,A/D用于地址/数据的选择,当其为0时,表示本操作为数据读或写;当其为1时,表示本操作为地址写。R/W用于读/写操作的选择,当其为0时,进行写,当其为1时,进行读。A[5:0]用于地址/数据的选择,当Bit7=0时,D[3:0]为数据半字节;D[5:4]为未用,命令字为8位,故命令字数据分二次读出或写入;当Bit7=1时,D[5:0]包含将要寻址的命令寄存器地址。

2 USB软件设计

USB的软件设计包括三方面:固件设计、驱动程序设计和主机端应用程序设计。

2.1 固件设计

所有基于微控制器及外围电路功能设备的正常工作都离不开固件的参与,固件的作用就是辅助硬件工作。没有固件的参与和控制,硬件设备无法实现预期的功能。USB设备也不例外,必须编写固件程序来辅助硬件完成USB的通信任务。由于采用不带MCU内核的USB接口芯片,USB的应用层协议应该通过对TMS320C6416的编程来实现,USB固件的加载必须靠DSP的控制CY7C68001来完成。在CCS中用C语言完成固件程序的编写,程序流程图如图2所示。

|

根据程序流程图,固件设计思路如下:

(1)初始化工作。包括设置一些特殊功能寄存器的初值,以实现所需的设备属性或功能,例如:配置端口、使能端点、开中断。该设计中,使CY7C68001工作于异步FIFO模式,将4 KB的FIFO对应到两个端点(Endpoint),即Endpoint2和Endpoint6。

(2)辅助硬件完成设备的重新列举过程。包括模拟设备的断开与重新连接,对接收到的设置包进行分析判断,从而对主机的设备请求做出适当的响应,完成主机对设备的配置任务。

(3)对中断的处理。CY7C68001有6个中断源,可以分别通过中断使能对寄存器的各位进行设置。一旦中断事件发生,CY7C68001的INT引脚就被置低,并且置中断使能寄存器的相应位(即中断使能寄存器同时充当中断标志寄存器,中断使能寄存器具有读写属性)。当中断发生时,中断标志寄存器的状态字映射到FD[7:0];中断发生后。DSP对CY7C68001简单的一次读操作即可获取中断信息,识别中断源并进行相应处理。相对于中断标志寄存器的读操作,其他对CY7C68001寄存器的读操作通常要先发送一次请求,并且收到READY响应后.才可以读取数据。

(4)数据的接收与发送。在读数据时,应首先判断CY7C68001的FIFO2是否为空,如果不为空,才将数据读进来。在写数据时,还要判断要写的数据个数是否为512 B的整倍数,如果不是,则使用PKTEND信号来标识数据包的结束。EP2和EP6分别对应存放USB需要上传与接收的数据。其中,EP2为OUT型,负责从主机接收数据;EP6为IN型,负责向主机发送数据。EP2和EP6均采用批量(BULK)传输方式,这种传输方式具有数据可靠,传输速率高等特点,特别适合大批量数据传输。部分关键代码如下:

DSP读端点2中的数据:

- 实现WUSB设备控制器的设计考虑因素(09-12)

- 基于USB2.0的高速无线数传接收设备的数据接收存储方法(09-09)

- 四种短距离无线监控解决方案的性能对比(09-16)

- Wibree:一个可供选择的新无线联网技术(11-07)

- TI 单芯片手机多媒体电话解决方案(12-01)

- 蓝牙技术硬件实现模式分析(01-11)