基于MEMS强链和FPGA的USB移动硬盘数据加解密系统

时间:09-25

来源:与非网

点击:

|

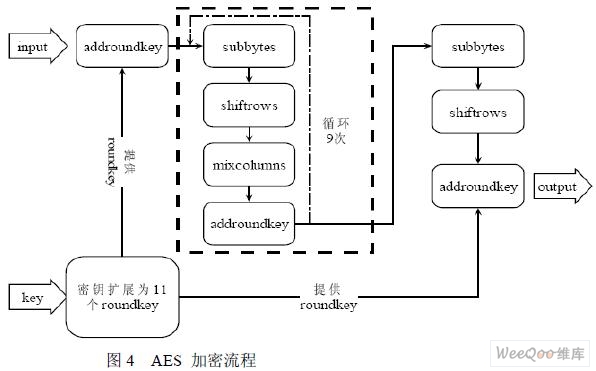

5. AES 加密模块的实现

AES 的设计原理可参考文献[1],下面只简单介绍算法过程。AES 是一个迭代的分组密码, 每一轮迭代称为一个轮变换,包括一个混合和三个代换:

(1)字节代换(SubBytes):利用S 盒对状态的每一个字节进行非线性变换。

(2)行移位(ShiftRow):对状态的每一行,按不同的位移量进行行移位。

(3)列混合(MixColumn):对状态中的每一列并行应用列混合,在最后一轮省略该步。

(4)扩展密钥加(AddRoundKey):与扩展密钥异或。 加密算法的流程如图4 所示。

相应的,解密算法使用逆序的扩展密钥,轮变换分别为InvSubByte,InvShiftRow, InvMixColumn,数据流程稍有不同。

我们设计的AES 加密运算模块以128 位为一个分组,完成一个分组的运算需要11 个时钟 周期。第1 个时钟周期,密钥扩展模块输出第1 个扩展密码,也就是初始密码本身;同时初始 变换模块用这个扩展密码对128 位明文作AddRoundKey 操作。

第2 个到第11 个时钟周期,密 钥扩展模块依次生成10 个扩展密码,同时,轮变换模块利用这些扩展密码对输入密文作10 个 轮次的轮变换,其中最后一轮缺少列混合操作,然后输出最终的密文,结束一个分组的运算。

6. 数据吞吐率分析

Ultra DMA 在模式2 下的数据传输率为33.33MB/s。由于FPGA 全局时钟频率为100MHz, 所以加解密一个128 位分组需要110ns。加上数据的输入和输出阶段各占用一个时钟周期,总共 需要130ns。所以加解密模块的数据处理速率约为61.54MB/s,完全能够达到实时处理的要求。

7. 结束语

本文提出了一种安全高效的USB 移动硬盘数据加解密系统。其中,MEMS 强链的应用开辟 了系统物理认证的新方向;Ultra DMA 协议接口的FPGA 实现大大提高了硬盘读写的吞吐率,同时AES 加解模块的处理速率又能完全满足Ultra DMA 传输带宽,两者的有机协作使得一种高 效的硬件加解密流水线得以实现。

USB MEMS FPGA 移动硬盘 数据加密 系统 相关文章:

- 实现WUSB设备控制器的设计考虑因素(09-12)

- 基于USB2.0的高速无线数传接收设备的数据接收存储方法(09-09)

- 四种短距离无线监控解决方案的性能对比(09-16)

- Wibree:一个可供选择的新无线联网技术(11-07)

- TI 单芯片手机多媒体电话解决方案(12-01)

- 蓝牙技术硬件实现模式分析(01-11)