基于SoC的实时信号处理系统中存储系统

时间:09-17

来源:EDN

点击:

在现代信息社会中,嵌入式系统由于其灵活性及方便性得到了越来越广泛的使用。采用SoC技术可以将整个系统集成到单个芯片之中,其具有体积小、重量轻、功耗小、IP复用等优点。SoC技术目前正成为嵌入式实时系统发展的一个趋势,得到越来越广泛的应用。

系统的纠错和容错能力具有十分重要的意义。这里的容错是指当部分存储器件损坏无法工作时,系统可以有效地利用冗余器件,通过硬件检测或软件指令配置,使存储系统能够继续正常工作。纠错是指当读写数据中出现一位或多位数据出错时,系统自动计算出正确数据的机制,通常情况下,是通过被动硬件冗余防止故障造成差错。常用的方法有三模冗余(TMR)、N模冗余、表决技术等。但此类方法所需附加硬件多,花费代价非常昂贵,同时造成功耗、重量及体积增大很多。当系统发生故障时,通过对整个系统进行替换来保证整个存储系统的可靠性;另一方面,此类方法由于欠缺灵活性,如果多个冗余部分同一位置上的芯片都发生故障,则整个系统仍然无法使用,备份效率也不是很高。

本文针对潜入式实时数字信号处理系统的特点,重新组织DDR存储颗粒的结构,添加冗余颗粒和相关寄存器,改写控制IP,设计了一种新的具有容错纠错自适应功能的二级冗余存储体系结构。它仅需增加少量的冗余器件就可以容忍系统中较多数目的器件故障。在系统没有故障的情况下,存储颗粒可以采用海明码等EDAC码进行纠错;当系统中部分器件出现故障时,系统可以通过软件配置或硬件自动检测,自动利用冗余模块进行容错;当故障进一步增多时,可以适当降低系统的纠错能力,若错误过多,还可以将原先用于纠错的颗粒改为用于容错,使系统能够继续正常地工作。通过数学模型的量化分析,新的存储系统容错方案可以有效地提高存储系统的可靠性。

存储系统容错方案系统结构

容错存储系统工作流程

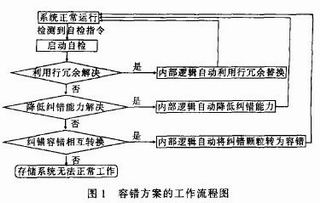

冗余存储颗粒排放方式采用二级冗余的组织形式,整个存储系统容错方案的工作流程如图1所示。

该容错方案具有以下几个特点:

(1)可变的纠错能力。系统支持海明码或CRC等EDAC码,并且当系统出现部分不可逆转故障时,可以自动降低纠错能力。比如,原先系统可以支持每16bit纠1bit错的能力,当存储颗粒出现部分错误时,可以降低为每32bit纠1bit错。

(2)系统自检和容错系统自修复。当系统出现不可逆转故障时,系统可以通过简单的软件命令实现系统错误自检,并自动利用冗余模块启动容错功能,使系统仍然保持正常工作。

(3)纠错能力与容错能力之间的转换。当系统故障的模块过多,冗余模块已经不能保证系统的正常工作,则系统可以自动将部分原先用于纠错的存储颗粒改为用于容错功能。这时,系统的纠错能力会下降或被放弃,但至少能保证系统继续基本正常的工作。

(4)采用行列二级冗余形式,首先利用冗余的行冗余进行纠错,行冗余消耗完毕再利用列冗余进行纠错。

容错存储系统的硬件支持

具有容错纠错能力的存储系统的结构图如图2所示。存储系统的容错方案和不考虑容错的存储系统相比,需要在原有模块的基础上进行修改并增加一些设计。主要包含以下几个方面:

(1)增加存储颗粒。为了实现存储系统的容错和纠错能力,增加一定数量的存储颗粒是必须的。在存储颗粒阵列中增加冗余的行列按照行列的二级冗余存储形式组织。为了适应SoC实时信号处理系统的特点,需要对存储系统颗粒阵列的信号连线进行有针对性的修改,从而使系统能通过软件配置或硬件自检来实现纠错或容错,并有效地支持包含纠错容错转换的总体方案。

(2)在寄存器堆中为容错系统分配一定的寄存器地址空间。这些寄存器地址空间由多个部分组成,主要包括系统工作状态寄存器,记录系统各个存储期间的状态;系统纠错方案配置寄存器,配置系统可以采用的纠错方式和纠错能力。

(3)增加纠错码编码解码模块具有容错功能的地址生成。纠错码可以采用多种方式,如海明码、CRC码等。具有容错功能的地址生成模块使系统可以根据容错寄存器的内容,重新生成数据的写入地址和读出地址。

(4)增加自测逻辑生成模块。当软件命令配置了寄存器开始进行自检时,自测逻辑不再处理总线上接收的命令,自动生成测试用代码和地址进行写读检测,使系统可以根据对存储颗粒的工作状态进行有效的分析,并且当发现硬件故障时,就修改寄存器空间中的相关寄存器,以便系统自动启动纠错和容错功能。

(5)修改地址变换和数据重组功能模块。修改后的数据重组需要依据寄存器空间中的故障情况对数据进行重新组织,以便达到容错和纠错的功能。

系统的纠错和容错能力具有十分重要的意义。这里的容错是指当部分存储器件损坏无法工作时,系统可以有效地利用冗余器件,通过硬件检测或软件指令配置,使存储系统能够继续正常工作。纠错是指当读写数据中出现一位或多位数据出错时,系统自动计算出正确数据的机制,通常情况下,是通过被动硬件冗余防止故障造成差错。常用的方法有三模冗余(TMR)、N模冗余、表决技术等。但此类方法所需附加硬件多,花费代价非常昂贵,同时造成功耗、重量及体积增大很多。当系统发生故障时,通过对整个系统进行替换来保证整个存储系统的可靠性;另一方面,此类方法由于欠缺灵活性,如果多个冗余部分同一位置上的芯片都发生故障,则整个系统仍然无法使用,备份效率也不是很高。

本文针对潜入式实时数字信号处理系统的特点,重新组织DDR存储颗粒的结构,添加冗余颗粒和相关寄存器,改写控制IP,设计了一种新的具有容错纠错自适应功能的二级冗余存储体系结构。它仅需增加少量的冗余器件就可以容忍系统中较多数目的器件故障。在系统没有故障的情况下,存储颗粒可以采用海明码等EDAC码进行纠错;当系统中部分器件出现故障时,系统可以通过软件配置或硬件自动检测,自动利用冗余模块进行容错;当故障进一步增多时,可以适当降低系统的纠错能力,若错误过多,还可以将原先用于纠错的颗粒改为用于容错,使系统能够继续正常地工作。通过数学模型的量化分析,新的存储系统容错方案可以有效地提高存储系统的可靠性。

存储系统容错方案系统结构

容错存储系统工作流程

冗余存储颗粒排放方式采用二级冗余的组织形式,整个存储系统容错方案的工作流程如图1所示。

|

该容错方案具有以下几个特点:

(1)可变的纠错能力。系统支持海明码或CRC等EDAC码,并且当系统出现部分不可逆转故障时,可以自动降低纠错能力。比如,原先系统可以支持每16bit纠1bit错的能力,当存储颗粒出现部分错误时,可以降低为每32bit纠1bit错。

(2)系统自检和容错系统自修复。当系统出现不可逆转故障时,系统可以通过简单的软件命令实现系统错误自检,并自动利用冗余模块启动容错功能,使系统仍然保持正常工作。

(3)纠错能力与容错能力之间的转换。当系统故障的模块过多,冗余模块已经不能保证系统的正常工作,则系统可以自动将部分原先用于纠错的存储颗粒改为用于容错功能。这时,系统的纠错能力会下降或被放弃,但至少能保证系统继续基本正常的工作。

(4)采用行列二级冗余形式,首先利用冗余的行冗余进行纠错,行冗余消耗完毕再利用列冗余进行纠错。

容错存储系统的硬件支持

具有容错纠错能力的存储系统的结构图如图2所示。存储系统的容错方案和不考虑容错的存储系统相比,需要在原有模块的基础上进行修改并增加一些设计。主要包含以下几个方面:

(1)增加存储颗粒。为了实现存储系统的容错和纠错能力,增加一定数量的存储颗粒是必须的。在存储颗粒阵列中增加冗余的行列按照行列的二级冗余存储形式组织。为了适应SoC实时信号处理系统的特点,需要对存储系统颗粒阵列的信号连线进行有针对性的修改,从而使系统能通过软件配置或硬件自检来实现纠错或容错,并有效地支持包含纠错容错转换的总体方案。

(2)在寄存器堆中为容错系统分配一定的寄存器地址空间。这些寄存器地址空间由多个部分组成,主要包括系统工作状态寄存器,记录系统各个存储期间的状态;系统纠错方案配置寄存器,配置系统可以采用的纠错方式和纠错能力。

(3)增加纠错码编码解码模块具有容错功能的地址生成。纠错码可以采用多种方式,如海明码、CRC码等。具有容错功能的地址生成模块使系统可以根据容错寄存器的内容,重新生成数据的写入地址和读出地址。

(4)增加自测逻辑生成模块。当软件命令配置了寄存器开始进行自检时,自测逻辑不再处理总线上接收的命令,自动生成测试用代码和地址进行写读检测,使系统可以根据对存储颗粒的工作状态进行有效的分析,并且当发现硬件故障时,就修改寄存器空间中的相关寄存器,以便系统自动启动纠错和容错功能。

(5)修改地址变换和数据重组功能模块。修改后的数据重组需要依据寄存器空间中的故障情况对数据进行重新组织,以便达到容错和纠错的功能。

- SoC面临挑战,智能分割顺势而起(11-07)

- 基于PL3200的CDMA扩频电力线载波通信系统设计(11-19)

- 基于SOCKS地IPv4向IPv6过渡技术(01-08)

- 基于GPRS的SOCKET通信的应用研究(01-15)

- 蓝牙技术硬件实现模式分析(01-11)

- 代理服务器------代理之间的级联(03-17)