基于TUSB6020的USB OTG接口设计

时间:08-25

来源:微计算机信息

点击:

USB开发者论坛发布了USB2.0补充规范USB OTG(On-The-GO),解决了两个关键的问题:一是双角色的USB外设,二是供电问题,从而实现了便携设备间无主机的数据传输 [1-2]。目前,TI公司推出的高速USB2.0 OTG双功能控制器TUSB6020,是一种小型解决方案,既能作为针对USB外设的功能控制器使用,又能作为点对点或点对多点通信中的主机/外设工作。本文在此基础上研TMS320DM6437与TUSB6020的USB OTG的接口设计方案。

1 TUSB6020的特性、内部结构及其工作原理

1.1 TUSB6020特性和内部结构 TUSB6020采用最小5×5mm封装,符合USBG2.0 OTG规范,具有以下关键特性:

SRP和主机流通协议HNP。

提供多种工作速率,包括 1.5Mbps低速率、12Mbps全速率和 480Mbps高速率。

VBUS短路的保护电路。

片上集成可切换的上拉和下拉电阻。

片上锁相环可降低高速时钟噪声。

电源耗电量小于100mW。

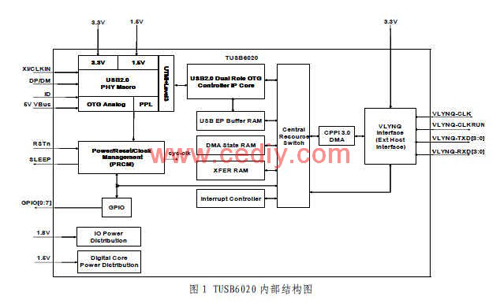

图1为TUSB6020的内部结构。TUSB6020主要模块有USB 2.0 PHY模块、电源/复位/时钟控制模块(PRCM)、USB2.0 OTG控制模块及VLYNQ外部主机接口模块等。功能参见文献[3]。

1.2 TUSB6020工作原理

TUSB6020工作状态分为复位状态、空闲状态和正常工作状态。在空闲状态下,USB2.0 PHY挂起;正常工作状态下,使能USB2.0 PHY,从而使能VBUS检测电路和ID检测电路。不妨设TUSB6020为OTG主机设备(A设备),对方USB设备作为OTG从机设备(B设备),分析对话请求协议SRP和主机通信协议HNP的工作过程。

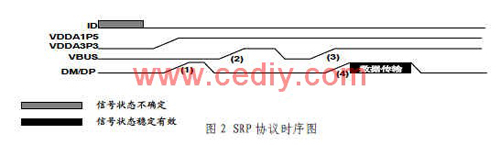

B设备向A设备发起SRP会话的条件是:(1)VBUS跌落到会话有效阀值0.8V以下;(2)DM/DP维持低电平SEO状态至少2ms。之后,B设备开始发起SRP请求,如图2所示。

工作步骤如下:(1)B设备将上拉电阻接入 DM/DP并持续5-10ms;(2)B设备驱动 VBUS足够长的一段时间直到 VBUS大于会话有效阀值0.8V;(3)A设备检测到 DM/DP或 VBUS升高,开启 VBUS电源给 B设备供电;(4)A设备复位总线对 B设备进行枚举配置,开始传输任务。

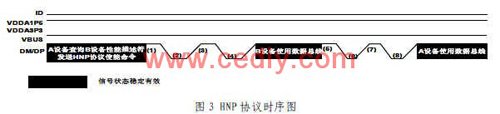

HNP协议用来控制A、B两设备主从角色的转换。A设备查询B设备的OTG性能描述符,以判断B设备是否为OTG设备,若B设备为OTG设备,返回有效的性能描述符,A设备向B设备发送Set feature命令,然后挂起总线,等待B设备的HNP请求。如图3所示。

工作流程可以归纳为:(1)A设备挂起总线,DM/DP为高电平;(2)B设备收到Set feature命令,在总线挂起后断开它的DM/DP上拉电阻,将总线释放到SEO状态;(3)A设备检测到SEO状态后响应,连接它的DM/DP上拉电阻;(4)B设备在检测到DM/DP变高后,开始以主机方式工作,B设备复位总线,开始使用总线;(5)B设备使用完总线后,停止总线活动挂起总线,DM/DP再次变为高电平;(6)A设备检测到总线空闲后,断开DM/DP上拉电阻;(7)B设备检测DM/DP变低后,连接DM/DP上拉电阻;(8)A设备等待DM/DP变高后,表明B设备已准备回到从机状态,A设备从新成为主机复位总线,开始使用总线。2 "达芬奇"处理器 TMS320DM6437与 TUSB6020的接口设计

TMS320DM6437是达芬奇技术中首批仅基于DSP的产品,集成有600MHz时钟的C64x+增强型DSP核心、视频处理子系统(VPS)以及丰富的外围接口,支持通用USB2.0和VLYNQ高速传输总线,以低于以往的价位提供了更高的处理性能。

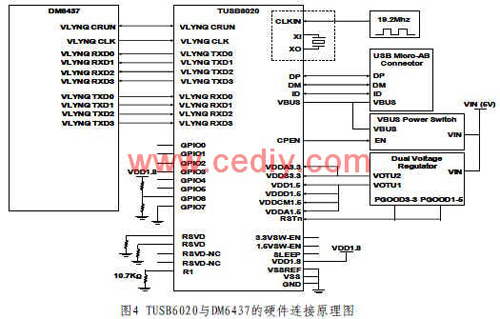

2.1 硬件设计 TUSB6020与 TMS320DM6437硬件连接的电路图如图 4所示。

TUSB6020的DM/DP、ID和VBUS引脚与USBmicroAB连接器相连,建立与对方 USB设备的物理连接,其中 VBUS 5V电压由 VBUS电源开关提供,CPEN连接至它 EN引脚用以提供电源开关使能信号。双电源调节器向 TUSB6020提供 3.3V和 1.5V的数字、模拟电压[4]。

VLYNQ接口引脚详细描述如下:(1)TUSB6020的 VLYNQ CLK接外部时钟,VLYNQ控制寄存器中的 CLKDIR比特位设置为 1,VLYNQ接口时钟由 DM6437系统时钟提供。(2)VLYNQ SCRUN为 VLYNQ时钟运行请求引脚,低电平表示允许 VLYNQ时钟运行,高电平表示传输事务结束,VLYNQ时钟运行停止。(3)TMS320DM6437写操作时,将数据压缩、地址编译,经串行编码后由 VLYNQTXD[0:3]发出,TUSB6020将数据进行串行解码和解压缩后读取地址,将数据写入指定寄存器。

(4)TMS320DM6437读操作时,由 VLYNQ TXD[0:3]发送读请求数据包,TUSB6020收到请求后,将数据压缩和串行编码后由 VLYNQ TXD[0:3]发往TMS320DM6437。(5)VLYNQ接口的数据收发与VLYNQ串行时钟同步。

1 TUSB6020的特性、内部结构及其工作原理

1.1 TUSB6020特性和内部结构 TUSB6020采用最小5×5mm封装,符合USBG2.0 OTG规范,具有以下关键特性:

SRP和主机流通协议HNP。

提供多种工作速率,包括 1.5Mbps低速率、12Mbps全速率和 480Mbps高速率。

VBUS短路的保护电路。

片上集成可切换的上拉和下拉电阻。

片上锁相环可降低高速时钟噪声。

电源耗电量小于100mW。

|

图1为TUSB6020的内部结构。TUSB6020主要模块有USB 2.0 PHY模块、电源/复位/时钟控制模块(PRCM)、USB2.0 OTG控制模块及VLYNQ外部主机接口模块等。功能参见文献[3]。

1.2 TUSB6020工作原理

TUSB6020工作状态分为复位状态、空闲状态和正常工作状态。在空闲状态下,USB2.0 PHY挂起;正常工作状态下,使能USB2.0 PHY,从而使能VBUS检测电路和ID检测电路。不妨设TUSB6020为OTG主机设备(A设备),对方USB设备作为OTG从机设备(B设备),分析对话请求协议SRP和主机通信协议HNP的工作过程。

B设备向A设备发起SRP会话的条件是:(1)VBUS跌落到会话有效阀值0.8V以下;(2)DM/DP维持低电平SEO状态至少2ms。之后,B设备开始发起SRP请求,如图2所示。

|

工作步骤如下:(1)B设备将上拉电阻接入 DM/DP并持续5-10ms;(2)B设备驱动 VBUS足够长的一段时间直到 VBUS大于会话有效阀值0.8V;(3)A设备检测到 DM/DP或 VBUS升高,开启 VBUS电源给 B设备供电;(4)A设备复位总线对 B设备进行枚举配置,开始传输任务。

HNP协议用来控制A、B两设备主从角色的转换。A设备查询B设备的OTG性能描述符,以判断B设备是否为OTG设备,若B设备为OTG设备,返回有效的性能描述符,A设备向B设备发送Set feature命令,然后挂起总线,等待B设备的HNP请求。如图3所示。

工作流程可以归纳为:(1)A设备挂起总线,DM/DP为高电平;(2)B设备收到Set feature命令,在总线挂起后断开它的DM/DP上拉电阻,将总线释放到SEO状态;(3)A设备检测到SEO状态后响应,连接它的DM/DP上拉电阻;(4)B设备在检测到DM/DP变高后,开始以主机方式工作,B设备复位总线,开始使用总线;(5)B设备使用完总线后,停止总线活动挂起总线,DM/DP再次变为高电平;(6)A设备检测到总线空闲后,断开DM/DP上拉电阻;(7)B设备检测DM/DP变低后,连接DM/DP上拉电阻;(8)A设备等待DM/DP变高后,表明B设备已准备回到从机状态,A设备从新成为主机复位总线,开始使用总线。2 "达芬奇"处理器 TMS320DM6437与 TUSB6020的接口设计

TMS320DM6437是达芬奇技术中首批仅基于DSP的产品,集成有600MHz时钟的C64x+增强型DSP核心、视频处理子系统(VPS)以及丰富的外围接口,支持通用USB2.0和VLYNQ高速传输总线,以低于以往的价位提供了更高的处理性能。

|

2.1 硬件设计 TUSB6020与 TMS320DM6437硬件连接的电路图如图 4所示。

|

VLYNQ接口引脚详细描述如下:(1)TUSB6020的 VLYNQ CLK接外部时钟,VLYNQ控制寄存器中的 CLKDIR比特位设置为 1,VLYNQ接口时钟由 DM6437系统时钟提供。(2)VLYNQ SCRUN为 VLYNQ时钟运行请求引脚,低电平表示允许 VLYNQ时钟运行,高电平表示传输事务结束,VLYNQ时钟运行停止。(3)TMS320DM6437写操作时,将数据压缩、地址编译,经串行编码后由 VLYNQTXD[0:3]发出,TUSB6020将数据进行串行解码和解压缩后读取地址,将数据写入指定寄存器。

(4)TMS320DM6437读操作时,由 VLYNQ TXD[0:3]发送读请求数据包,TUSB6020收到请求后,将数据压缩和串行编码后由 VLYNQ TXD[0:3]发往TMS320DM6437。(5)VLYNQ接口的数据收发与VLYNQ串行时钟同步。

TUSB6020 USB2 0 SRP HNP USB OTG 相关文章:

- USB 2.0标准(04-14)

- USB2.0规范的主要特点(04-14)

- USB设备驱动程序的设计(05-20)

- 基于SOPC的高速数据采集系统的分析与设计(01-01)

- 基于USB2.0的高性能移动存储设备的设计(02-05)

- IEEE 802.16x标准和机制(08-28)