简易USB与LVDS接口转换器

时间:08-19

来源:国外电子元器件

点击:

|

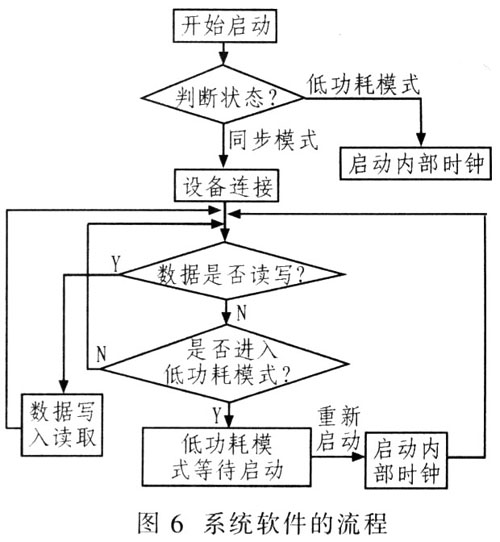

4 系统软件设计

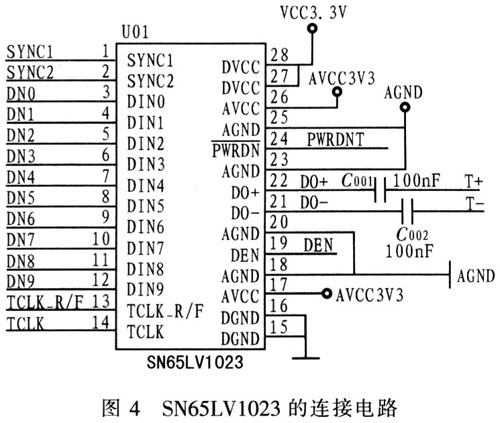

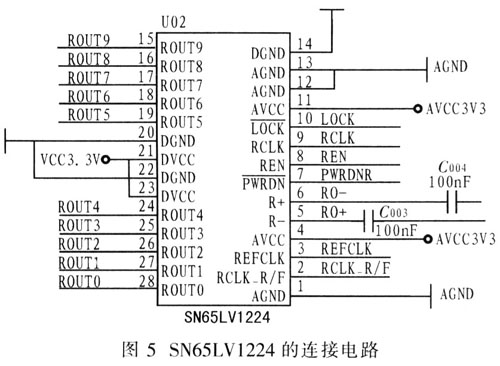

利用可编程逻辑门阵列FPGA转换协议数据,由于系统使用USB3300可将USB协议物理层信号转换成8位并行信号,而使用SN65LV 1023与SN65LV1224则将低压差分信号LVDS转换成10位并行信号,这样大大简化FPGA的编程。

FPGA编程只需通过控制引脚,控制两个并行信号的输入输出即可,同时可将数据的读写操作模块化,从而进一步简化系统编程。 系统软件设计流程如同6所示。由于遵循USB协议,在一段时间不进行任何操作时则进入低功耗模式。而USB3300也拥有这一特性。在一定时间系统不进行任何的读写操作,USB3300将进入低功耗模式,此时USB3300会自动关闭锁相环时钟输出。

所以在系统启动后,首先判断USB3300的状态,如果在低功耗模式下,则控制STP信号开启内部时钟,进入到同步模式。 设备连接成功后,随时判断是否应该进行读写操作,若需要,则进入读写操作模块,实现读写操作后又开始判断读写。等待一段时间不执行读写操作后,USB3300则进入低功耗模式,关闭锁相环,等待下次读写操作时再重新启动内部时钟。

|

|

5 结论

采用专用转换器USB3300,SN65LV1023,SN65LV1224分别将USB协议物理层的差分信号和LVDS的低压差分信号转换成并行信号,并通过FPGA编程实现协议编程的转换。该系统设计较为简单,并且系统拓展较简单,可易于实现USB接口、LVDS接口对多种接口的转换。

由于串口通信协议的物理层信号较为复杂,FPGA直接与其物理层信号进行数据交互比较难以实现,难以做到时序同步,而采用专用的转换器将串行信号转换成并行数据信号,则大大简化逻辑门阵列编程。该系统合理使用USB3300和SN65LV1023与SN65LV1224接口器件使得逻辑门阵列的编程易于实现,也可使用其他的专用转换器,实现不同接口的转换。

USB LVDS FPGA 通用串行总线 SN65LV1023 相关文章:

- 实现WUSB设备控制器的设计考虑因素(09-12)

- 基于USB2.0的高速无线数传接收设备的数据接收存储方法(09-09)

- 四种短距离无线监控解决方案的性能对比(09-16)

- Wibree:一个可供选择的新无线联网技术(11-07)

- TI 单芯片手机多媒体电话解决方案(12-01)

- 蓝牙技术硬件实现模式分析(01-11)