基于DSP的高性能通用并行弹载计算机设计与实现

时间:06-19

来源:21IC

点击:

摘要:为满足弹上信号处理领域不断增长的任务需求并适应不同的应用场合,设计高性能通用并行计算机,进而构建各类信号处理系统是一种趋势。基于时共享总线和分布式两种并行结构的理论分析,结合信号处理系统的特点,设计了一种高性能通用并行弹载计算机,它具有标准化、模块化、可扩展、可重构、混合并行模式、多层次互联的特性,通过构建典型弹载计算机验证了这些特性。

关键词:弹载计算机;并行处理;TS201;FPGA

0 引 言

随着技术的发展,在导弹控制和通信等领域,需要处理的任务规模越来越大。虽然随着VLSI技术的发展,已产生了运算能力达每秒几十亿次的处理器,但还远远不能满足这些领域的需求。而VLSI技术的发展已受到其开关速度的限制,进一步提高处理器主频遇到的困难越来越大。为此,把用于大型计算机的并行处理技术应用到信号处理中来,在信号处理系统中引入并行多处理器技术是必然趋势。传统弹载计算机一般针对特定场合,先确定算法,再根据算法确定系统结构,由于系统结构与算法严格相关,因此通用性较差。随着一些标准技术(标准板型、接口、互联协议等)在弹上控制系统中的应用,设计标准化、模块化的通用型计算机成为了可行。而且所设计的还要可扩展、可重构,进而根据不同的应用场合和算法构建各种弹载计算机系统。

1 并行弹载计算机处理结构模型

普遍的两种并行处理结构如图1所示,一种是共享总线结构,另一种是分布式并行结构。其中,P(Proces-sor):处理器;M(Memory):存储器;MB(Memory Bus):存储器总线;NIC(Network Interface Circuitry):网络接口电路。共享总线结构中多个处理器P经由高速总线连向共享存储器,每个处理器等同地访问共享存储器、I/O设备和操作系统服务。分布式并行结构中多个处理节点通过高通信带宽、低延迟的定制网络互联,每个处理节点都有物理上的分布存储器,节点间通过消息传递相互作用。

并行处理的目的是采用多个处理器同时对任务处理,从而减小任务执行时间,它主要反映在加速比(S)和并行效率(E)上。加速比是指对于一个特定应用,并行算法的执行速度相对串行算法加快了很多倍。效率则是针对每个处理器来衡量的。依据并行处理中可扩放性(Sealability)评测的等效率度量标准可从理论上评测这两种结构。

首先考虑共享总线结构。设 分别是并行系统上第i个处理器的有用处理时间和额外开销时间。设每个处理器上子任务的运算量和通信量之比为r,即平均r次运算中有一个数据需要交换。总线被p个处理器轮流访问,tio。是处理器完成一次总线存取所需的相对时间,等效为处理器运算能力和总线访问能力之比。一般情况下,总的处理时间和额外开销时间如下:

分别是并行系统上第i个处理器的有用处理时间和额外开销时间。设每个处理器上子任务的运算量和通信量之比为r,即平均r次运算中有一个数据需要交换。总线被p个处理器轮流访问,tio。是处理器完成一次总线存取所需的相对时间,等效为处理器运算能力和总线访问能力之比。一般情况下,总的处理时间和额外开销时间如下:

假设任务均匀分成p部分,就有:Te=pt。在最坏情况下,p个处理器总是同时访问总线,考虑最后得到总线访问权的处理器:

Tp是每个处理器上并行算法运行时间,在最坏情况下,Tp=Te+To。设问题规模W为最佳串行算法完成的计算量,即W=Te,加速度比:

显而易见,共享总线系统的并行效率随着处理器数目p的增大而下降。

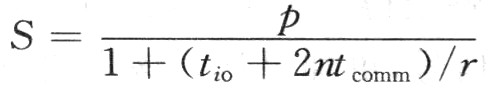

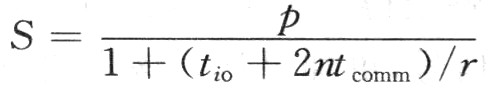

而在分布式并行系统中,理想情况下任一时刻都可有两个处理器通过其通信口相互交换数据,设一个通信口传送一个数据的相对时间为tcomm,等效为处理器运算能力和通信口传输能力之比。同时,假设每次交换还需对本地存储器访问。这样就有通信开销:

和处理规模p成线性关系,并行效率与p无关。

以上讨论的是假设任意两个处理器之间可以直接进行数据交换,而在实际情况下,尤其是处理器数目p多于处理器的通信口数量时,两个非直接相连的处理器之间的数据交换所需开销与其经过的路径成正比关系。但这并不影响以上讨论的公式。因为在规则网络拓扑结构中最大或平均路径是一个定值n,那么这时,分布式并行系统的加速比公式为:

可见,在这种情况下分布式并行系统同样能获得线性加速比。由以上理论分析可知,共享总线并行结构适合共享存储编程模型,进行细粒度的并行处理,但其扩展性能较差,处理器的数目有限,单机处理性能有限;分布式并行结构采用消息传递的机制,适合进行粗粒度的并行处理,便于大规模的系统扩展,提供强大的整体性能。

2 弹载计算机的设计实现

由于弹上信号处理算法的复杂性,信号处理系统具有复杂多样的并行处理模式,如基于空间的数据并行处理、基于时间的流水并行处理等。另外,弹上计算机系统具有多种类型的数据流,如原始数据流(A/D采集之后的数据流)、中间数据流(各处理节点之间传递的数据流)、定时同步信号以及控制数据流等。这些不同的数据流的传输带宽不同,因此系统中要有与这些不同数据流相匹配的互联网络。

高性能通用并行弹载计算机是构建信号处理系统的基础。它除了选用高性能的处理器外,为了具有通用性,还要具有标准化、模块化、可扩展、可重构的特点,以便构建各类控制和信号处理系统。同时为了适应控制和信号处理系统复杂并行处理模式和多种数据流的特点,它要具有混合的并行模式和多层次的互联网络。基于这些要求和上文中对并行处理结构模型的理论分析,笔者选用当前业界最高性能的浮点DSP芯片TS201和大规模FPGA,设计了一个标准化、模块化、可扩展、可重构、混合并行模式、多层次互联的高性能通用并行弹载计算机。图2是其结构框图。

关键词:弹载计算机;并行处理;TS201;FPGA

0 引 言

随着技术的发展,在导弹控制和通信等领域,需要处理的任务规模越来越大。虽然随着VLSI技术的发展,已产生了运算能力达每秒几十亿次的处理器,但还远远不能满足这些领域的需求。而VLSI技术的发展已受到其开关速度的限制,进一步提高处理器主频遇到的困难越来越大。为此,把用于大型计算机的并行处理技术应用到信号处理中来,在信号处理系统中引入并行多处理器技术是必然趋势。传统弹载计算机一般针对特定场合,先确定算法,再根据算法确定系统结构,由于系统结构与算法严格相关,因此通用性较差。随着一些标准技术(标准板型、接口、互联协议等)在弹上控制系统中的应用,设计标准化、模块化的通用型计算机成为了可行。而且所设计的还要可扩展、可重构,进而根据不同的应用场合和算法构建各种弹载计算机系统。

1 并行弹载计算机处理结构模型

普遍的两种并行处理结构如图1所示,一种是共享总线结构,另一种是分布式并行结构。其中,P(Proces-sor):处理器;M(Memory):存储器;MB(Memory Bus):存储器总线;NIC(Network Interface Circuitry):网络接口电路。共享总线结构中多个处理器P经由高速总线连向共享存储器,每个处理器等同地访问共享存储器、I/O设备和操作系统服务。分布式并行结构中多个处理节点通过高通信带宽、低延迟的定制网络互联,每个处理节点都有物理上的分布存储器,节点间通过消息传递相互作用。

并行处理的目的是采用多个处理器同时对任务处理,从而减小任务执行时间,它主要反映在加速比(S)和并行效率(E)上。加速比是指对于一个特定应用,并行算法的执行速度相对串行算法加快了很多倍。效率则是针对每个处理器来衡量的。依据并行处理中可扩放性(Sealability)评测的等效率度量标准可从理论上评测这两种结构。

首先考虑共享总线结构。设

分别是并行系统上第i个处理器的有用处理时间和额外开销时间。设每个处理器上子任务的运算量和通信量之比为r,即平均r次运算中有一个数据需要交换。总线被p个处理器轮流访问,tio。是处理器完成一次总线存取所需的相对时间,等效为处理器运算能力和总线访问能力之比。一般情况下,总的处理时间和额外开销时间如下:

分别是并行系统上第i个处理器的有用处理时间和额外开销时间。设每个处理器上子任务的运算量和通信量之比为r,即平均r次运算中有一个数据需要交换。总线被p个处理器轮流访问,tio。是处理器完成一次总线存取所需的相对时间,等效为处理器运算能力和总线访问能力之比。一般情况下,总的处理时间和额外开销时间如下:

假设任务均匀分成p部分,就有:Te=pt。在最坏情况下,p个处理器总是同时访问总线,考虑最后得到总线访问权的处理器:

Tp是每个处理器上并行算法运行时间,在最坏情况下,Tp=Te+To。设问题规模W为最佳串行算法完成的计算量,即W=Te,加速度比:

显而易见,共享总线系统的并行效率随着处理器数目p的增大而下降。

而在分布式并行系统中,理想情况下任一时刻都可有两个处理器通过其通信口相互交换数据,设一个通信口传送一个数据的相对时间为tcomm,等效为处理器运算能力和通信口传输能力之比。同时,假设每次交换还需对本地存储器访问。这样就有通信开销:

和处理规模p成线性关系,并行效率与p无关。

以上讨论的是假设任意两个处理器之间可以直接进行数据交换,而在实际情况下,尤其是处理器数目p多于处理器的通信口数量时,两个非直接相连的处理器之间的数据交换所需开销与其经过的路径成正比关系。但这并不影响以上讨论的公式。因为在规则网络拓扑结构中最大或平均路径是一个定值n,那么这时,分布式并行系统的加速比公式为:

可见,在这种情况下分布式并行系统同样能获得线性加速比。由以上理论分析可知,共享总线并行结构适合共享存储编程模型,进行细粒度的并行处理,但其扩展性能较差,处理器的数目有限,单机处理性能有限;分布式并行结构采用消息传递的机制,适合进行粗粒度的并行处理,便于大规模的系统扩展,提供强大的整体性能。

2 弹载计算机的设计实现

由于弹上信号处理算法的复杂性,信号处理系统具有复杂多样的并行处理模式,如基于空间的数据并行处理、基于时间的流水并行处理等。另外,弹上计算机系统具有多种类型的数据流,如原始数据流(A/D采集之后的数据流)、中间数据流(各处理节点之间传递的数据流)、定时同步信号以及控制数据流等。这些不同的数据流的传输带宽不同,因此系统中要有与这些不同数据流相匹配的互联网络。

高性能通用并行弹载计算机是构建信号处理系统的基础。它除了选用高性能的处理器外,为了具有通用性,还要具有标准化、模块化、可扩展、可重构的特点,以便构建各类控制和信号处理系统。同时为了适应控制和信号处理系统复杂并行处理模式和多种数据流的特点,它要具有混合的并行模式和多层次的互联网络。基于这些要求和上文中对并行处理结构模型的理论分析,笔者选用当前业界最高性能的浮点DSP芯片TS201和大规模FPGA,设计了一个标准化、模块化、可扩展、可重构、混合并行模式、多层次互联的高性能通用并行弹载计算机。图2是其结构框图。

- 讲解Oracle中并行处理技术原理深入分析 (06-19)

- Oracle数据库并行处理技术剖析(08-24)

- 网上有朵开放的“云”(09-17)

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 面向大众市场的千兆位级收发器(05-04)