基于CPLD的键盘控制器设计

时间:05-20

来源:EDN

点击:

0 引 言

由于CPLD的可再编程性质,可以将同一装置用于不同的键盘和产品,而收到高产量、低成本的效果,同时也节约了单片机的资源以做它用。可再编程的特点辅之简便易用的设计工具,使设计可以进行晚期更改,提高了产品设计的灵活性,降低了风险。在单片机应用系统中,利用键盘接口输入数据,是实现现场实时调试、数据调整和各种参数设置最常用的方法。单片机的外围键盘扩展电路有多种实现方式,例如直接利用单片机的I/O接口,或者采用8255A接口芯片,就可以实现外围键盘的扩展功能。但是,在这些方法中,键盘扩展电路需要占用单片机的资源对按键进行监控和处理,这对要求高实时性处理的单片机系统是不容易实现的。为了解决这一问题,可以使用专用键盘接口芯片来扩展键盘子系统。但是这类专用键盘接口芯片在使用灵活性方面尚有欠缺,尤其当用户需要实现某些特定功能时,其缺点更为明显。针对上述问题,在此提出一种基于Lattice公司LC4128V的4×4键盘接口芯片设计。采用的软件开发环境是IspLEVER。

l 开发环境介绍

IspLEVER是Lattice公司最新推出的一套EDA软件。设计输入可采用原理图、硬件描述语言、混合输入3种方式,它能对所设计的数字电子系统进行功能仿真和时序仿真。编译器是此软件的核心,能进行逻辑优化,将逻辑映射到器件中去,自动完成布局与布线,并生成编程所需要的熔丝图文件。软件中的Constraints Editor工具允许经由一个图形用户接口选择I/O设置和引脚分配。lspLEVER软件提供给开发者一个简单而有力的工具,用于设计所有Lattice可编程逻辑产品。

2 键盘控制器设计

2.1 基于LC4128V的4×4键盘控制器设计

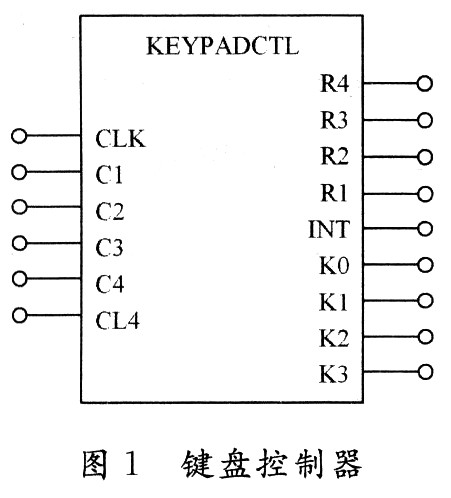

图1给出基于Lattice公司的可编程逻辑器件LC4128V的4×4键盘控制器(KEYPADCTL)设计。

2.2 内部原理图及其主要部分的工作原理

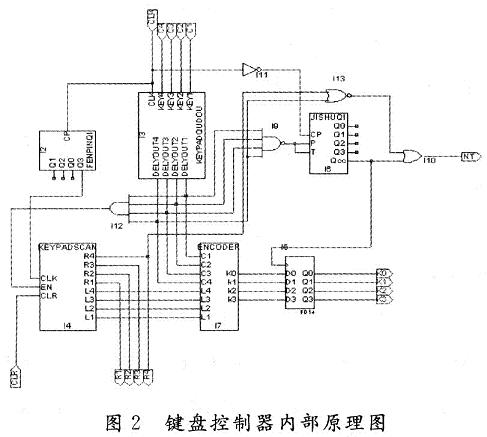

键盘控制器内部由键盘扫描电路、编码器电路、键盘去抖动电路、分频器电路、计数器电路和键值锁存器组成,如图2所示。

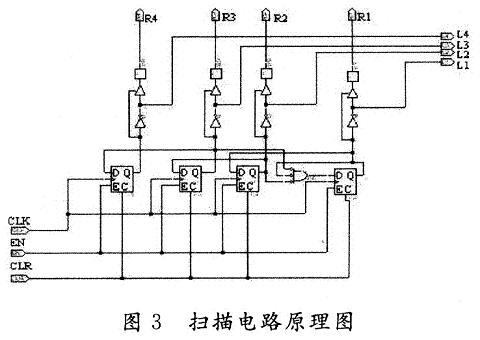

通过这样的处理既满足设计的需要,又起到对器件保护的作用。EN是扫描电路的使能输入端,高电平有效。它通过去抖动后的列回复线相与得到。当有按键按下时,相应的列线将被置低。相与的结果为低,这使扫描电路停止扫描,等待控制器对扫描结果进行处理,得到相应的键值送入键值锁存器,等待单片机读取。这样做的好处是可防止控制器漏掉按键的读取。根据调试得知,键盘扫描时钟信号最好是去抖电路时钟的四分频以上。所以CLK是通过对去抖电路的时钟进行分频得到的。图3给出实现扫描电路的具体原理图。

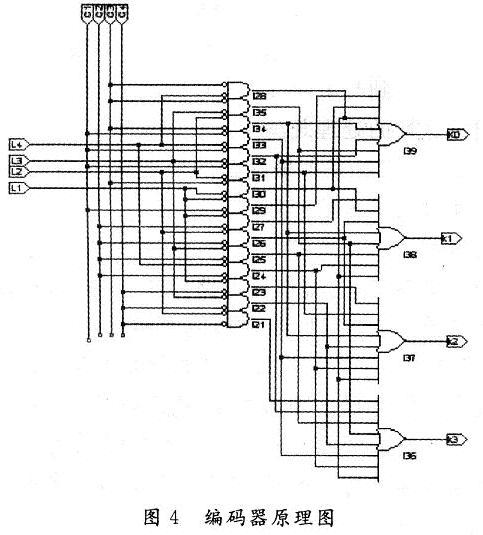

(2)该设计中采用4×4的键盘,有16个按键状态,再加上一个没有键按下的状态共有17个状态,而4位二进制数只能表示16个状态。为了解决这个问题,将R4和L4或非后再与计数器产生的中断信号相或,产生一个单片机中断。当按下最后一个键时,键盘控制器便产生1个中断,让单片机来读取这个按键值0000(在没有键按下时也是这个状态),从而区分了无按键状态和最后一个按键按下的状态。这样在编码的时候只需考虑前15个键的状态信息。最终可用4位二进制数表示所有按键状态。图4给出实现编码器的具体原理图。

由于CPLD的可再编程性质,可以将同一装置用于不同的键盘和产品,而收到高产量、低成本的效果,同时也节约了单片机的资源以做它用。可再编程的特点辅之简便易用的设计工具,使设计可以进行晚期更改,提高了产品设计的灵活性,降低了风险。在单片机应用系统中,利用键盘接口输入数据,是实现现场实时调试、数据调整和各种参数设置最常用的方法。单片机的外围键盘扩展电路有多种实现方式,例如直接利用单片机的I/O接口,或者采用8255A接口芯片,就可以实现外围键盘的扩展功能。但是,在这些方法中,键盘扩展电路需要占用单片机的资源对按键进行监控和处理,这对要求高实时性处理的单片机系统是不容易实现的。为了解决这一问题,可以使用专用键盘接口芯片来扩展键盘子系统。但是这类专用键盘接口芯片在使用灵活性方面尚有欠缺,尤其当用户需要实现某些特定功能时,其缺点更为明显。针对上述问题,在此提出一种基于Lattice公司LC4128V的4×4键盘接口芯片设计。采用的软件开发环境是IspLEVER。

l 开发环境介绍

IspLEVER是Lattice公司最新推出的一套EDA软件。设计输入可采用原理图、硬件描述语言、混合输入3种方式,它能对所设计的数字电子系统进行功能仿真和时序仿真。编译器是此软件的核心,能进行逻辑优化,将逻辑映射到器件中去,自动完成布局与布线,并生成编程所需要的熔丝图文件。软件中的Constraints Editor工具允许经由一个图形用户接口选择I/O设置和引脚分配。lspLEVER软件提供给开发者一个简单而有力的工具,用于设计所有Lattice可编程逻辑产品。

2 键盘控制器设计

2.1 基于LC4128V的4×4键盘控制器设计

图1给出基于Lattice公司的可编程逻辑器件LC4128V的4×4键盘控制器(KEYPADCTL)设计。

2.2 内部原理图及其主要部分的工作原理

键盘控制器内部由键盘扫描电路、编码器电路、键盘去抖动电路、分频器电路、计数器电路和键值锁存器组成,如图2所示。

通过这样的处理既满足设计的需要,又起到对器件保护的作用。EN是扫描电路的使能输入端,高电平有效。它通过去抖动后的列回复线相与得到。当有按键按下时,相应的列线将被置低。相与的结果为低,这使扫描电路停止扫描,等待控制器对扫描结果进行处理,得到相应的键值送入键值锁存器,等待单片机读取。这样做的好处是可防止控制器漏掉按键的读取。根据调试得知,键盘扫描时钟信号最好是去抖电路时钟的四分频以上。所以CLK是通过对去抖电路的时钟进行分频得到的。图3给出实现扫描电路的具体原理图。

(2)该设计中采用4×4的键盘,有16个按键状态,再加上一个没有键按下的状态共有17个状态,而4位二进制数只能表示16个状态。为了解决这个问题,将R4和L4或非后再与计数器产生的中断信号相或,产生一个单片机中断。当按下最后一个键时,键盘控制器便产生1个中断,让单片机来读取这个按键值0000(在没有键按下时也是这个状态),从而区分了无按键状态和最后一个按键按下的状态。这样在编码的时候只需考虑前15个键的状态信息。最终可用4位二进制数表示所有按键状态。图4给出实现编码器的具体原理图。

(3)键盘去抖动电路主要由2个DQ触发器和1个基本RS触发器组成。当有键按下时,理想情况下相应的列线应该是一直保持低电平。

但是实际应用中不可避免地产生抖动,此时列回复线将发生长短不等的高电平跳跃现象。键盘去抖电路就是去除这样抖动的高电平对按键键值检测带来的干扰。为了消除这样的干扰,去抖电路采用两级延时策略。

只要抖动的高电平持续时间在去抖电路的2个时钟周期之内,这种抖动是不会被引进编码电路的。键盘去抖电路的具体原理图实现如图5所示。

- 基于DSP与CPLD的多通道数据采集系统的设计(09-22)

- DSP和CPLD的空间瞬态光辐射信号实时探测研究(01-24)

- 基于CPLD的RS-232串口通信实现(04-23)

- USB数据采集系统中DMA数据传输的实现(06-17)

- 简易USB接口卡的设计和实现(04-21)

- G.723.1在DSP数字对讲机基带系统中的应用(01-14)