高速数据采集系统中的存储与传输控制逻辑设计

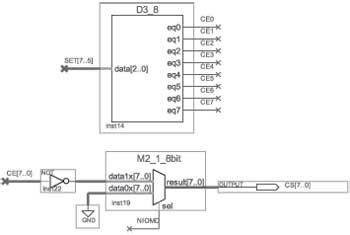

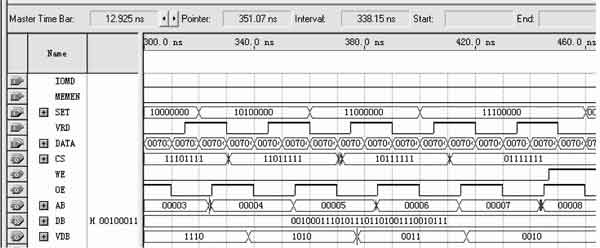

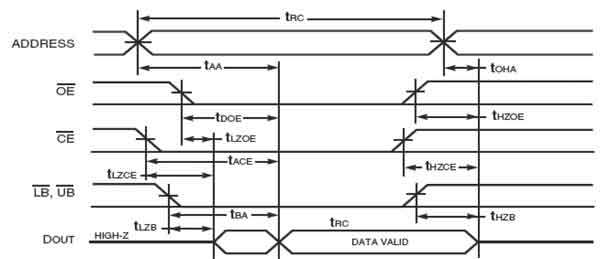

图4 RAM的读数据时序图 对于单片RAM的操作比较简单,但是要将数据顺序写入8片RAM中,就要求对上一片RAM写操作完成后,系统能够设置下一个待操作的RAM 有效,128位数据线分别对应8片RAM的数据线,由于地址线和读写使能线公用,则需要分别设置每个RAM的片选,以区别当前操作是针对哪一个RAM。片 选信号可以由译码器产生。读操作时设置相应RAM的片选有效,即可读出存储的数据,而进行写操作时,则可以设置所有的RAM片选有效,将采集到的数据同时 并行的写入8片RAM中。根据这些描述,片选信号的设计如图5所示。NIOMD为操作的状态信号,说明当前的操作是读状态或是写状态,读数据情况下设置为 1,片选信号分别有效,写数据情况下设置为0,所有RAM均处于片选有效状态下,可以同时写入数据。这样的设计也是为了配合系统的需求,一般的,读取数据 的速度相对于写数据来说还是要快一些的。

|

- LVDS技术及其在多信道高速数据传输中的应用(01-15)

- WCDMA的信道支持 (01-19)

- 基于对等模型的新型光因特网技术介绍(01-05)

- 城域传输网络业务结构特点与发展分析(上)(01-12)

- 城域传输网络业务结构特点与发展分析(下) (01-12)

- 浅析城域传输网的应用 (01-14)