高速数据采集系统中的存储与传输控制逻辑设计

随着信息科学的飞速发展,数据采集和存储技术广泛应用于雷达、通信、遥测遥感等领域。在高速数据采集系统中,由ADC转换后的数据需要存储在存储器 中,再进行相应的处理,保证快速准确的数据传输处理是实现高速数据采集的一个关键。由于高速ADC的转换率很高,而大容量RAM相对ADC输出速度较慢, 保持高速数据存储过程的可靠性、实时性是一个比较棘手的问题。对于数据采集系统中的大容量高速度数据存储、传输,本文提出一种基于FPGA的多片RAM实 现高速数据的存储和传输的方案,并应用于1GS/s数据采集系统中,实现了以低成本RAM完成高速实时数据存储系统的设计。

方案选择

高速的数据采集速度是保证数据采集精度的标准,但往往在数据处理时并不需要以同样的速度来进行,否则对硬件的需求太高,成本也较高。这就需要有一个数据缓存单元,将数据有效地存储,再根据系统需求进行数据处理。

通常构成高速缓存的方案有三种。第一种是FIFO(先进先出)方式。FIFO存储器就像数据管道一样,数据从管道的一头流入,从另一头流 出,先进入的数据先流出。FIFO具有两套数据线而无地址线,可在其一端写操作而在另一端读操作,数据在其中顺序移动,因而能够达到很高的传输速度和效 率,且由于省去了地址线而有利于PCB板布线。缺点是只能顺序读写数据,不易灵活控制,而且大容量的高速FIFO非常昂贵。

第二种是双口RAM方式。双口RAM具有两套独立的数据、地址和控制总线,因而可从两个端口同时读写而互不干扰,并可将采样数据从一个端口 写入,而由控制器从另一个端口读出。双口RAM也能达到很高的传输速度,并且具有随机存取的优点,缺点是大容量的高速双口RAM的价格很昂贵。

第三种是高速SRAM切换方式。高速SRAM只有一套数据、地址和控制总线,可通过三态缓冲门分别接到A/D转换器和控制器上。当A/D采 样时,SRAM由三态门切换到A/D转换器一侧,以使采样数据写入其中。当A/D采样结束后,SRAM再由三态门切换到控制器一侧进行读写。这种方式的优 点是SRAM可随机存取,同时较大容量的高速SRAM有现成的产品可供选择。

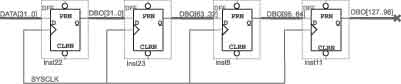

从降低成本上考虑,采用第三种方式实现大容量数据存储功能。结合1GS/s数据采集系统的要求,存储深度为4MB。选择ISSI公司的静态RAM,由8片IS61LV25616构成4MB测试数据的存储,系统结构如图1所示。

图1 数据存储原理框图 数据存储设计

|

- LVDS技术及其在多信道高速数据传输中的应用(01-15)

- WCDMA的信道支持 (01-19)

- 基于对等模型的新型光因特网技术介绍(01-05)

- 城域传输网络业务结构特点与发展分析(上)(01-12)

- 城域传输网络业务结构特点与发展分析(下) (01-12)

- 浅析城域传输网的应用 (01-14)