WCDMA系统基带处理的DSP FPGA实现方案

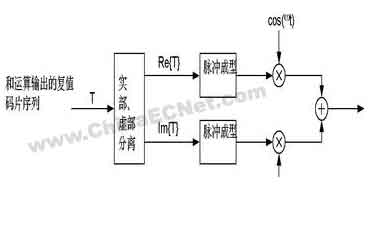

图3 下行链路调制 实现方案基带数据处理的电路结构 本文提出了"DSP+FPGA线性流水阵列结构"的实现方案:使用DSP与大规模FPGA协同处理基带发送数据。该处理单元以DPS芯片为核心,构造一个小的DSP系统。 在基带处理单元中,低层的信号预处理算法处理的数据量大,对处理速度的要求高,但运算结构相对比较简单,因而适于用FPGA进行硬件实现,这样能同时兼顾速度及灵活性。相比之下,高层处理算法的特点是所处理的数据量较低层算法少,但算法的控制结构复杂,适于用运算速度高、寻址方式灵活、通信机制强大的DSP芯片来实现。 DSP处理器利用其强大的I/O功能实现单元电路内部和各个单元之间的通信。从DSP的角度来看,可重构器件FPGA相当于它的协处理器。DSP通过本地总线对FPGA进行配置、参数设置及数据交互,实现软硬件之间的协同处理。DSP和FPGA各自带有RAM,用于存放处理过程所需要的数据及中间结果。除了DSP芯片和可重构器件FPGA外,硬件设计还包括一些外围的辅助电路,如FLASH EEPROM、外部存储器等。其中,FLASH EEPROM中存储了DSP的执行程序;外部存储器则作为FPGA的外部RAM扩展,用于存放数据处理过程中所需的映射图样。 基带处理单元的需求估计 基带处理单元的需求估计主要包含以下两个方面: 各个业务传输通道的数据处理: 以无线信道承载的最高业务速率384Kbps为例进行分析。根据3GPP协议TS25.211,为支持该种速率业务所要求的信道比特速率最大不超过 960K(对应扩频增益SF=8,每10ms帧内的比特数是9600bits)。系统在1个10ms帧内所要处理的最大数据量为: Wmax= 9600bits 根据3GGP 协议TS 25.212 V2.2.0规定的下行数据基带处理流程(图1所示),并按固定位置复用的方式进行处理,每个数据比特须经过最多10个环节的处理过程,分别是: 综合考虑上述两个方面,则整个基带数据处理的等效需求是: 在384Kbps业务信道加随路信令的处理中,384bpsK业务数据由DSP通过同步高速接口以DMA方式递交给FPGA,在FPGA中处理;而随路信令因其数据量小,在FPGA处理384Kbps业务数据时,随路信令数据在DSP中同时处理。此方法减少了数据处理时间,提高了处理速度。 结语 |

- 基于IXP421的VoIP网关及其性能测评(10-02)

- 新一代移动通信系统的关键技术(10-26)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 设计基于TMS320LF2407的低功耗中文人机界面 (04-16)

- USB接口芯片的原理及应用 (04-15)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)