1.2V高线性度低噪声折叠混频器设计

fdcp时, Vdd,min比常规反相器更小,适用于更低的工作电压。

1. 3 性能分析

1. 3. 1 增益

假设本振信号LO为理想方波信号, 则该混频器(如图1)的增益可表示为:

gm n是M1 和M2 的跨导, gm p是M3 和M4 的跨导, R 即负载电阻RL 的值。因为开关管的漏极电流很小,所以负载电阻值可以适当增加,由式( 1)知,混频器的增益将随之提高。值得注意的是, 增大负载电阻值的同时必须保证节点A 的直流电压足够使得M1 和M2 工作在饱和区。

1. 3. 2 噪声系数

假设本振信号为理想方波信号,并考虑镜像频率的影响,噪声系数的表达式为:

RS 为源阻抗, RL 为负载电阻值, 系数γn 对长沟道晶体管来说等于2 /3,对于亚微米MOSFET,γn 的值较大。由式(2)知,只要选择合理的偏置电压Vrfdcn、Vrfdcp和M1~M4的宽长比, 噪声系数随着跨导的增加而减小。

1. 3. 3 线性度

如果节点A (见图1)的电压过高,开关管将会关断。也就是说,如果M1 和M3 的电流很大,M1 和M2的输出端电压也增大,这样就会关断开关管M7 和M6或者M5 和M8。开关管进入线性区,影响混频器的线性度,所以降低节点A 的电压,并让开关管远离线性区 ,即Vgs≈Vth ,能提高混频器的线性度。

2 电路仿真

该混频器设计基于SM IC 0. 18 μm标准CMOS工艺,用Advanced Design SySTem软件进行电路设计与仿真。电源电压1. 2 V; RF频率为2. 5 GHz,功率为- 30 dbm; LO频率为2. 6 GHz,本振信号的电压摆幅VLO = 600 m Vpp。

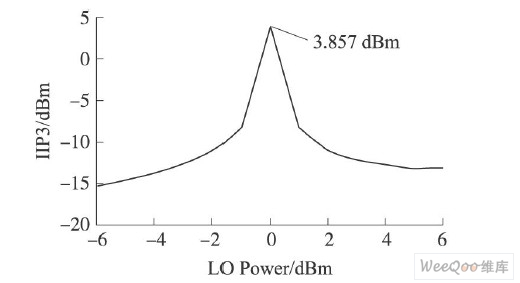

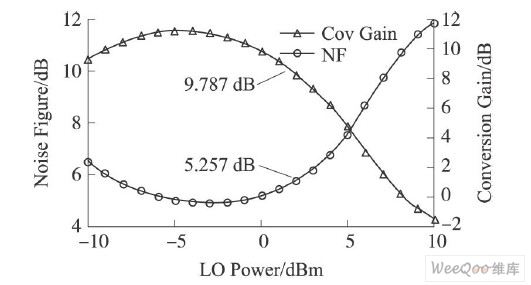

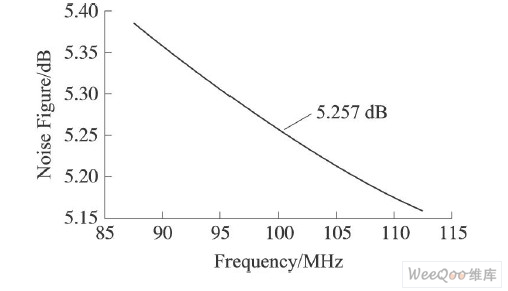

图3是三阶交调点( IIP3)随本振功率变化曲线,在本振功率为0 dBm时, IIP3达到最大值3. 857dBm。当本振功率大于或小于0 dBm时, IIP3都会急剧下降。图4是噪声系数(NF)和转换增益(Con2version Gain)随本振功率变化曲线,本振功率为- 3dBm时,噪声系数达最小值4. 982 dB,本振功率为- 5 dBm时,转换增益达到最大值11. 23 dB。考虑到混频器的整体性能,必须采取折衷,所以选择本振功率为0 dBm,此时,噪声系数为5. 257 dB,转换增益为9. 787 dB。图5是当本振功率为0 dBm时,噪声系数随输出频率变化曲线,噪声系数随着输出频率的增加不断减小,在输出频率为100 MHz时,噪声系数为5. 257 dB。

图3 IIP3随本振功率变化曲线。

图4 NF与转换增益随本振功率变化曲线。

图5 NF随输出频率变化曲线。

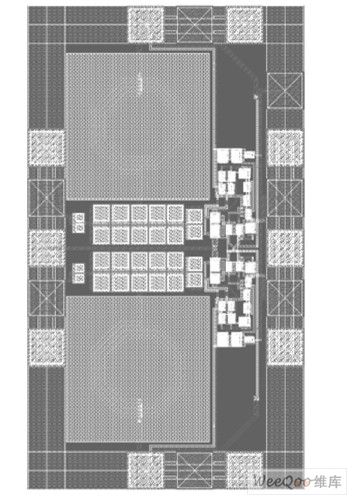

图6是该折叠混频器的版图,该版图用CadenceVirtuoso Layout editor进行设计及优化。RF输入端的匹配网络与IF输出端的buffer都集成在了片内,版图面积556μm ×966μm。

图6 折叠混频器版图。

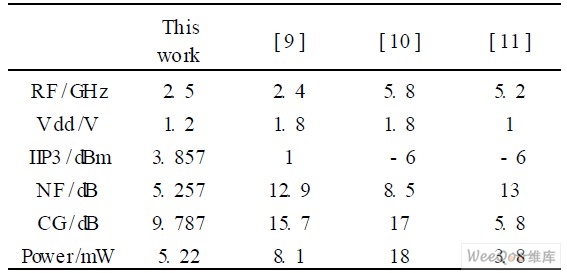

表1是本文设计的折叠混频器整体性能的仿真结果,并与其他发表的论文做了比较,可以看出该混频器具有高线性度,低噪声的优点。

表1 混频器性能总结与比较

3 总结

本文采用交流耦合互补跨导级成功设计了一种适用于低电源电压下工作的折叠混频器。仿真结果表明,该混频器具有高线性度、低噪声的优点。

混频器设计 相关文章:

- 创新混频器让混频设计更有保障(04-18)