先进纳米IC设计面临新的寄生电路提取挑战

为进一步提高性能,新的架构针对精度要求较低的地方(例如上金属层)采用了具备高度可扩展性的基于规则的技术。表1展示了Calibre xACT如何针对不同的几何形状和层来自动挑选合适的提取技术。

表1:CALIbRe xACT平台针对特殊应用采取的最佳提取技术。

这 些创新方法相结合能够将提取性能提高三倍,或实现8个CPU每小时4~8百万个网络的处理量,以及达到最尖端的晶圆代工厂签核要求的精度。通过新的 Calibre xACT架构,提取有1百万个台的IP仅需15分钟,而带2千万网络的全芯片提取也能在一夜之间完成。对于更大型的设计,可以通过增加额外的CPU来处 理。

针对需要很多提取角落的设计,这款新平台执行同步多角落提取,各个角落的运行时间减少了15%~20%,而精度丝毫不受影响。由于该平台使用确定性技术,单一角落和多角落运行始终能够提供同样的结果,Monte Carlo方法则无法做到如此。

选择性网络处理和网表简化

加速周转时间并同时减少管理数据量的另一个方法是选择性网络处理技术。通过该 技术,设计人员可以为各个网络选择特定的寄生模型,从而定制针对仿真而生成的数据量(图3)。设计人员可以按各个网络逐个选择分散RCC(带耦合电容)、 RC(不带耦合电容)、C或R,或依各层来控制提取。例如,为降低仿真时间,同时顾及大功率网络和地线网络的寄生效应,设计人员可以提取仅包含过孔电阻而 排除金属层电阻的VDD和VSS网络。这个功能特别有用, 因为过孔对电源/地线网络形成的电阻最大。该功能可以加快仿真速度,同时维持所需的设计裕量。

图3:Calibre xACT具备选择性处理功能。这个例子采用不同网络模型针对不同网络类型生成了网表。对于电源(VDD)网络和地线(VSS)网络,仅将过孔电阻提取到网表中。RCC模式提取了关键的差分对网络PLUS和MINUS,所有其他网络将只包含总电容值。

另 一个节省时间的方法是从单个寄生参数提取数据库(或提取运行)生成多个网表。这个方法可用于生成多种网表格式和具备多寄生模式的网表,其可以根据各个网络 进行控制。通过这种方法,设计人员无需在每次生成不同网络时运行提取,从而节省了时间;此外,还可以针对单个提取运行进行多个布局后分析。例如,设计人员 可以在设计的所有网络上执行单个RCC提取运行;然后以RCC网络模型生成所有信号网络的SPICE网表,以进行时序分析;最后生成一个DSPF格式的仅 包含电阻的网表,以用于电迁移分析。

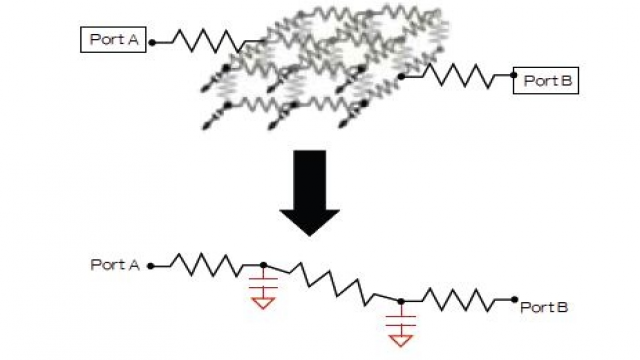

仿真器性能在很大程度上取决于网表的大小,而寄生元件可能使网表尺寸成数量级增加。精度 越高意味着寄生参数越多,但电路就会更加复杂,分析时间也会更长。这就是灵活的网表简化技术至关重要的原因—它可以尽可能地减少用于布线后仿真的寄生电路 数据量,仅生成所需的寄生电路数据(图4)。这样不仅提高了仿真性能,还减少了分析时间和收敛性问题。

图4:设计人员可以微调网表简化设置,按照需要来控制精度水平和网表尺寸。在这个例子中,过孔阵列被极大地缩小,从而使仿真速度加快,同时又不影响精度。

总结

数字、定制、模拟或RF设计团队在处理任何节点,特别是16nm或更小的节点时,需要有比以往所有工具速度更快、精度更高、灵活性更强的提取工具。为应对挑战,EDA供应商需采用基于更高级架构和算法的新提取工具来获得所需功能。

- 帮你看懂已经全面攻占iPhone的FinFET(08-19)

- FinFET布局和布线要经受的重大考验(04-04)

- 单收/单发RS-232接口芯片 ADM101E及其应用(01-25)

- 设计高性能、低成本的笔记本电脑处理器电源 (05-12)

- 半导体器件寿命测试(05-26)

- 用于家用电器、控制器和交流电源的协同式电路保护(06-15)