全差分BiCMOS采样/保持电路仿真设计

0 引言

随着数字技术、微机和模数转换技术的研究与进展,作为模拟和数字信号接口电路的模数转换器(ADC)得到了广泛应用。由于ADc中的重要组成单元——采样/保持(S/H)电路的精度和速度直接决定ADC的性能,所以设计高性能S/H电路是改善ADC性能的重要一环。目前研究S/H电路的文献有不少,例如文献[1]设计了电荷翻转型S/H电路,但该文未考虑开关导通电阻对电路性能的影响,S/H电路具有较大的失真;文献[2]设计的S/H电路虽然考虑开关对电路的影响,但未曾考虑全差分运放电路共模输出电压对静态工作点的影响。为了解决传统S/H电路失真大和静态工作点不稳定的问题,采用0.25 μm BiCMOS工艺,设计了一款高速率、高精度的10位全差分BiCMOS S/H电路。文中改进型自举开关电路和双通道开关电容共模反馈电路(CMFB)设计具有创新性。

1 整体设计思路

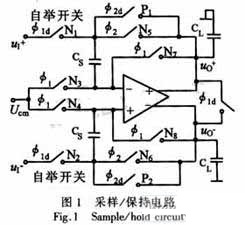

图1为s/H电路的结构,Ucm为运放的共模输入电压,采样开关N1和N2设计为图2的自举开关,N3~N8采用NMOS开关,以上开关在相应的时钟信号为高电平时闭合。当φ1d为高电平、φ2为低电平时,输入电压uI通过电容CS进行采样;当φ1d低电平、φ2高电平时,电路进入保持阶段,uI经过采样电容CS和反馈通道连接至运放输出端,输出端负载由CL驱动,这样的采样电路结构使反馈系数接近于1。根据推导,在采样阶段,CMOS开关工作在线性区,采样开关管栅-源电压UGS与输入电压uI的关系为

UGS=UCP-UIsin(2πfIt)(1)

式中:UI为输入电压uI的幅值;fI为输入信号频率;UCP为采样时钟信号的幅值。在保持阶段φ2导通,CS的下极板直接与运放的输出端相连接,uI通过采样电容传输至输出端;当采样阶段过渡到保持阶段时,CMOS器件出现沟道电荷注入,同时在保持阶段由于电容耦合,会出现时钟反馈通道。因此利用下极板采样技术降低开关动作时对采样信号的影响,两个阶段CS上存储的正负电荷相互抵消,从而消除了运放工作时产生的误差。另外,选取合适的时间常数RC可以提高采样速率。

2 输入端栅-源自举开关的设计

当uI=UIsin(2πfIt)时,图1中的CMOS开关N1和N2的导通电阻与输入信号呈非线性关系,因此对连续时间信号采样时,会产生信号失真和幅度波动,这限制了采样速率和S/H电路的开启时间;且CMOS开关的栅.源电压越大,导通电阻越小。若将N1和N2设计为栅-源自举开关,就能保证N1和N2的栅-源电压不超出VDD,则导通电阻接近于常数并使失真降到最低。于是设计的栅.源自举开关如图2所示,CP为高电平时,VN1和VN2导通,电容C3充电至VDD,VN8和VN6导通,VN7关闭。CP为低电平时,VN1,VN2和VN8断开,VP4,VH5和VN7导通,C3上电压就经过VP4,VN7和VN5加至VP5上,其栅-源电压UGS=VDD;当CP为高电平时,栅-源自举开关Nl和N2导通,CP为低电平时栅.源自举开关N1和N2关断。在CP相VN6导通,A点电压较高,开关VN1和VN2呈现阻性负载,因此存在着如图2中虚线所示的泄漏电流ID,严重制约运放增益的提高。采用VP6进行钳位,使得CP相VN6处于关闭状态,并使采样开关N1和N2自举电压提高10%,泄漏电流减小40%。由于存在着衬偏效应,所以N1和N2的导通电阻不能保持为定值,采用小尺寸的VP5不但可减小导通电阻,而且能改善线性度。图2中输出缓冲电容C4起到隔离作用。

3 全差分运放的设计

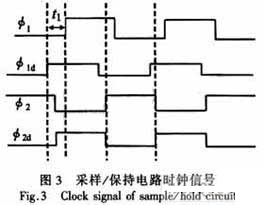

对于图1采样/保持电路,在φld时刻对输入差分信号采样,φ2时刻将前一时刻存储于Cs上的电荷传到输出端,φ1为下极板采样开关N3和N4的控制时钟信号,它比时钟信号φ1d延时t1,使开关N3和N4先于开关N1和N2开通或关断。图3为图1电路所要求的时钟信号:设计的S/H电路是一个零阶采样电路,因为在采样阶段N7和N8都导通,输人和输出信号具有相同的直流分量;在采样和保持阶段电压变化不明显,但每一个采样阶段运放的输出电压都要置为0 V。因此,所设计全差分运放除了具有高速、高精度性能外,还要有输入、输出端短路的特性。

图4为多增益级折叠式共栅-共源运放电路,采用Q1和Q2双极型晶体管(BJT)差动输入方式,共栅-共源镜像电流源VP3和VP4,VP1和VP2作为有源负载,藉此提高运放的电压增益;采用Q3,Q4和Q5,Q6共基-共射电路作为运放的差动输出级,以增强运放的负载驱动能力并具有高速特性;开关电容构成共模反馈电路(CMFB),可使运放的输出信号和输入信号的直流分量相等;UB1,UB2,UB3和UB4为偏置电压。转换时间tC和建立时间tS分别约为采样周期TS的1/8和3/8。经过计算,当fS为250 MHz时,tC=0

- 高速差分ADC驱动放大器AD8137及其应用(01-17)

- 基于开关电容共模反馈理论分析(05-30)

- 基于Multisim的差分放大电路仿真分析(06-14)

- 差分放大器中的不匹配效应及消除方法(08-19)

- 全差分驱动器开启高速ADC的高性能应用之门(04-19)

- 平稳地远程传送高速模拟/数字转换数据(06-28)