用于时间交织ADC的高精度开环跟踪保持电路设计

了P管的漏源电压,提高了输出电阻,从而改善了增益和线性度。与传统的级串型源随器相比,由于漏端跟栅端电压几乎保持相同的电压相位和幅度,栅漏电容也降低了,故输入电容不但不会增加,反而降低了。而低的输入电容又避免了对高频输入信号的衰减。

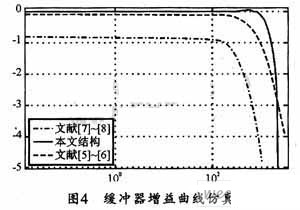

参考零极点分析,在适当的设计参数下,由于左半平面零点的存在,使得增益曲线中有一个上翘的过程,从而展宽了缓冲器带宽,图4所示为其缓冲的增益曲线。从图4中给出的三种结构的增益仿真结果可以看出,在驱动相同的负载情况下,本文的输出缓冲器结构增益和有效增益带宽都明显好于其他两种结构。

4 仿真结果分析

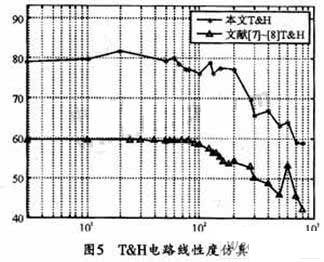

该电路采用0.18μCMOS工艺模型,输入信号峰峰值为1.6Vpp,采样频率为400 MHz,可在HSPICE仿真条件下进行设计仿真。图5给出了T&H电路的无杂散动态范围仿真结果。从图中可以看出,本T&H电路结构的静态精度为79 dB,相对于交叉耦合对结构的59 dB静态精度,有近20 dB的提高。电路的动态精度可以达到58.7 dB,相对提高了16.5 dB。可见,本文介绍的T&H电路无论是静态精度,还是动态精度都优于以往文献中的结构性能,而且在面积功耗方面也都有所缩小。

5 结束语

本文采用0.18 μm CMOS工艺设计了一种适用于TI-ADC的高速、低功耗开环T&H电路。仿真结果表明:通过采用高线性度自举开关和高增益高带宽输出缓冲器可以显著改善开环T&H电路的精度。可在400 MHz的采样频率,1.6Vpp的输入信号范围,799.8047 MHz信号输入频率下,最终获得9.5位的近似精度,同时电路功耗仅10.56mW。由此可见,本开环T&H电路的设计简单,功耗低,能够较好满足较高线性度的应用要求。(顾川,冯朝坤,刘元,于奇 电子薄膜与集成器件国家重点实验室)

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 12位串行A/D转换器的原理及应用开发(10-09)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 深入解析:模拟前端模/数转换器的三种类型 (11-26)