无绝缘移频自动闭塞系统中采集系统设计

时间:01-15

来源:互联网

点击:

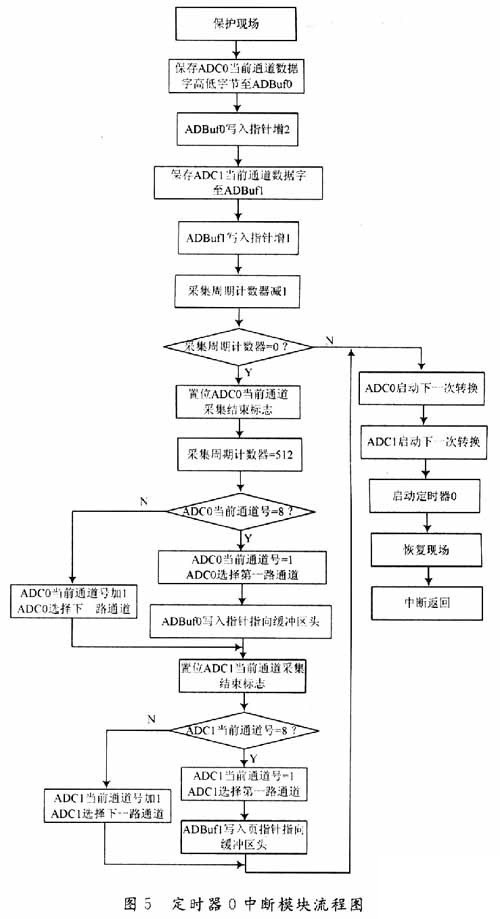

交流模拟输入的电压有效值。定时器0中断模块流程见图5。

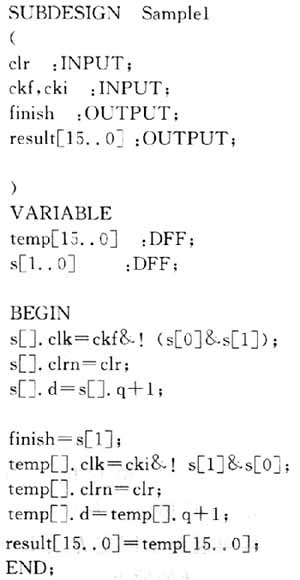

6.2 CPLD程序设计

CPLD程序是在MaxPlusⅡ开发环境下采用AHDL硬件描述语言和图形混合编写,限于篇幅,这里只给出其中一路低频采集的AHDL代码。

7 结语

该系统采用单片机内部集成ADC实现交流模拟量采集,同时利用C2PLD强大的数字处理功能和高密度集成的特点,降低了硬件成本,简化了电路设计,配合软件编程的灵活性和可扩充性,在实际生产和现场运用中带来了很好的经济和社会效益。在对测量精度要求不高的其他应用中,也不失为较好的选择。(现代电子技术 作者:田 霞)

- 影响绝缘电阻测量值的主要因素(10-26)

- 小电流接地系统单相接地故障选线方法研究(05-29)

- 电力变压器固体绝缘故障诊断(11-26)

- IC检测常识简介(03-30)

- 18脉波H级绝缘干式整流变压器(05-30)

- 基于LTC4310设计的绝缘双向I2C总线通信技术(04-14)