基于E类射频功率放大器设计

有效降低Miller 电容的影响,提高输入-输出之间的隔离度。 两个谐振网络中: Cd1 和L d1 构成的谐振器调谐在ω 处, Cd 3 和Ld 3 构成的谐振器调谐在3ω 处。 通过适当地调谐这四个参数,确保谐振网络对二次谐波短路,输出电路为基波和三次谐波叠加, 从而获得E 类放大器所需的近似方波驱动信号。在电路性能测试中我们发现,由于准F 类放大器 结构的开关电压峰峰值可达到2Vd1,因此增益驱动级的电源电压可以大大降低,从而可以有效减 少整个电路的直流功耗,提高电路的整体效率。

3.4 级间匹配网络

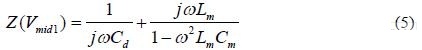

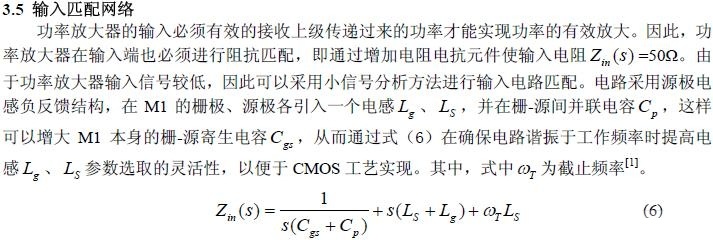

级间匹配网络需要匹配前一级器件的输出阻抗和后一级器件的输入阻抗,应选择高增益的级 间拓扑,并实现平坦的增益响应。级间匹配还应具备级间隔直流功能,通常加入隔直电容Cd 。 电路并联电感 Lm 可使功率输出级输入端看到的MOS 管寄生电容Cm 减小,从而提高电压传输效 率[5]。级间匹配等效电路如图4 所示,从增益驱动级输出端看到的等效阻抗为:

增益驱动级的方波信号是由基波和三次谐波叠加而成,因此通过公式(5)要确保增益驱动 级输出端看到的三次谐波和基波等效阻抗必须具有相同的容性或感性,否则会由于相位相反无法 形成方波。此外,测试中我们还发现Cd 值对传输效率影响比较敏感,为提高电压传输效率, Cd 一般需要取较大值。

4 仿真分析

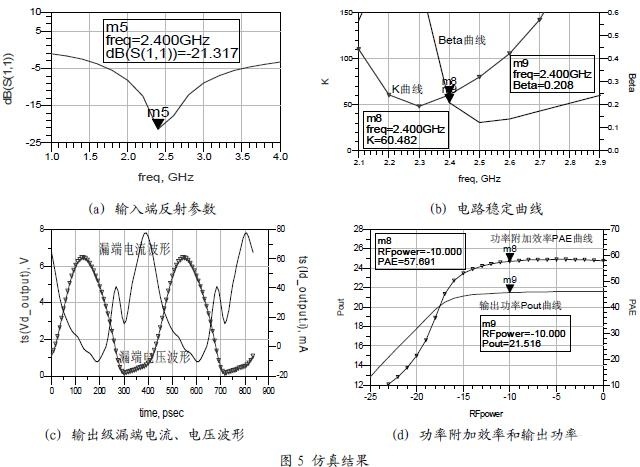

本设计基于0.18μm CMOS 工艺,充分考虑了片上电感品质因数不高、电感值较小和占有面 积较大的局限条件下,实现了电路的全片集成。在2V 电源电压条件下利用ADS2005A 进行仿真, 仿真结果如图5 所示。

当电流Id 趋于零时电压Vd达到峰值,而当电流Id 达到峰值时电压Vd趋于零,这与理想E 类开关 模式功率放大器的输出目标基本吻合,从而实现电路较大功率和较高效率的输出。图(d)表明,电 路在输入功率为-10dBm 时的输出功率约为21.5dBm,功率附加效率达到了57.69%的较好结果, 相应功率增益为31dB。

在性能仿真过程中我们发现,电路各级的阻抗匹配对电路的影响都非常大,阻抗匹配是电路 设计成败的关键。采用Load-Pull 技术是获取最佳输出匹配负载和预测晶体管输出功率和效率的 有效且便捷的手段。此外,输出晶体管尺寸对整体电路的输出功率和效率有着密切的联系,存在 最佳尺寸,使得电路主要性能达到最优化,但相应对电路的工作条件如驱动级电源电压等的要求 更高,因此需要折中考虑。

5 结论

本文的创新点在于在输入匹配晶体管栅-源间并接电容 Cp 极大的提高了在片电感选择的灵 活性;同时采用准F 类放大器作为驱动级,获得了E 类功率放大器所需要的方波驱动信号。本文 设计的E 类开关模式功率放大器达到了全集成、高效、大功率输出的目的,与国内外设计相比达 到先进水平[3-5]。随着CMOS 工艺和电感工艺的不断改进,由该技术实现的功率放大器在未来无 线通信领域必将有着广泛的应用前景。

- D类MOSFT在发射机射频功放中的应用(11-18)

- 单片射频收发芯片A7105的原理与应用(10-12)

- LDO电源管理模块的分析及其在数字模拟射频系统中的应用(01-26)

- 如何完善您的射频采样解决方案?(11-26)

- 核磁共振系统中射频开关设计(01-04)

- 基于MATLAB仪器控制工具箱的SAW标签阅读器系统设计(06-24)