CMOS音频功率放大器的旁路电压控制电路设计

电压时,比较器输出高电平,M19截止,电路停止对旁路电容充电,同时M21导通。此时C点的电压为:

式中:VC+为M21导通后电容上的电压;VC-为M21导通前的电容上的电压;τ为时间常数,τ=(RB+R)C;RB为B点到地的等效电阻。可以看到在一段时间后,旁路电容上的电压将近似等于B点电压,即VDD/2,则得到所需的旁路电压。同时,考虑到音频功率放大器上电、掉电的"POP"噪声是由旁路电压的瞬间跳变引起的,所以可以适当的增大旁路电容以增大旁路电压的上升、下降速度,起到减少"POP"噪声的作用。

当PD为高电平时.M16截止,电路不工作。

2 仿真结果

该使设计采用Candence Spectre仿真工具进行仿真,所采用的工艺是华润上华O.5μm的N阱CMOS工艺典型模型。

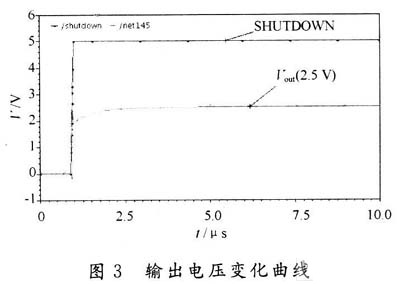

图3为该设计中旁路电压的输出变化曲线。"SHUTDOWN"引脚低电平有效,输出曲线在电路从关断状态转为工作状态时会出现一个小突刺,这是由于旁路电容上的电压比节点C略高,电容会有一个小的放电过程。在常温下,输出约在3.4μs处开始稳定在2.5 V。当t=7.5μs时,输出为2.501 6 V,其误差为O.064%。电路的静态功耗为O.685 mW。

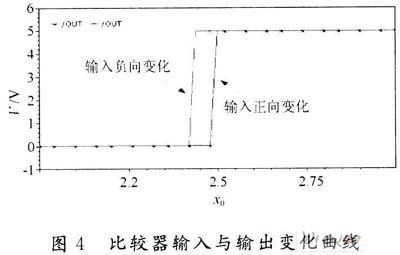

图4为电压比较器的正端电压从2.0~3.O V变化以及从3.O~2.0 V变化时,比较器的输出变化曲线。可以看出,比较器的正向阈值电压,负向阈值电压。与的不等说明引入迟滞后电路抑制噪声的能力明显增强。

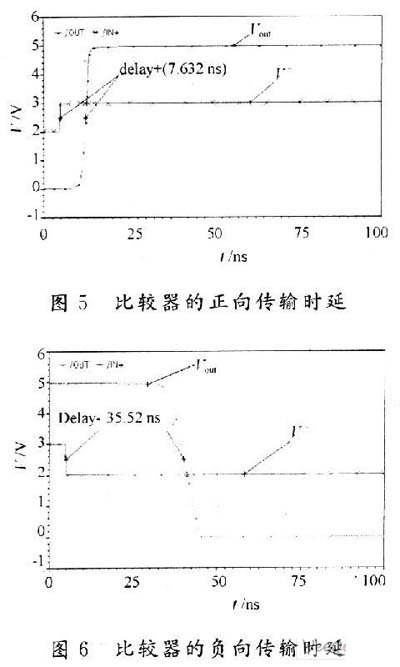

图5和图6分别为比较器的正向传输时延和负向传输时延。由图可知,比较器的正向传输时延为7.632 ns,负向传输时延为35.32 ns。对于大部分的芯片而言,这个数量级的延迟是可以忽略的。

3 结语

从上面的仿真结果可以看出,该设计的旁路电压控制电路可以产生输出稳定的旁路电压,且具有一定的噪声抑制能力。此外,整个电路的静态功耗低,信号的延迟时间较短,可以广泛应用于各种音频放大器电路中。

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- CMOS求和比较器在PWM开关电源控制中的应用(11-27)

- 如何将CMOS LDO应用于便携式产品中(01-15)

- 2.5 Gb/s 0.35μmCMOS光接收机前置放大器设计(01-22)

- 用于下一代移动电话的电源管理划分(08-28)

- 不同电源供电的器件间的桥接(04-27)