利用多通道ADC使系统性能达到更先进水平

引言

就像兔子诱惑狗赛跑一样,兔子必须要比狗跑的快,要求最严格的数据采集系统的性能自然要高于民用模数转换器(ADC)。这些极严格的要求推动IC制造商及其用户的发展,出现许多满足高端数据采集系统需求的"增强性能"的创新方法。

其中一种方法是通过采用多通道ADC填充转换器的"时隙"来大幅度增加采样速率、降低噪声或扩展动态范围。随着给定带宽和分辨率下的单个ADC的成本、尺寸和功耗的降低,并且随着多个转换器(通常封装在一起)的应用越来越多,该方法变得越来越切实可行。

本文将讨论两种多通道方法:信号平均--保证采样速率不变,增加分辨率;时间交织——保证分辨率不变,提高采样速率。采用这两种方法的产品已经诞生,例如ADI公司的AD10678(16 bit,80 MSPS ADC)和AD12500(12 bit,500 MSPS ADC)。

信号平均

信噪比(SNR,以 dB为单位),是成像和雷达等应用中的关键性能指标。这些系统中使用的ADC可能会受到许多外部噪声源的影响,包括时钟噪声、电源噪声和布线引入的耦合数字噪声。只要不相关噪声源的平方和的平方根(RSS)小于ADC固有量化噪声,输出平均就会有效地降低总体本底噪声。

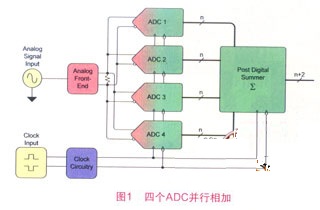

那些需要较高SNR的系统通常使用数字后处理器将多个ADC通道的输出加和。信号直接相加,而来自单独ADC(假设不相关)的噪声采用RSS加和,因此输出加和提高了总体SNR。四个ADC输出的加和会提高6 dB SNR,即1 LSB。AD6645 14 bit 80 MSPS ADC规定有效位数(ENOB)为12。图1示出四个AD6645的输出加和增加了2 bit分辨率和1 bit性能。

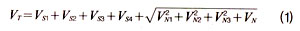

每个ADC的输入包含一个信号项(VS)和一个噪声项(VN)。对四个噪声电压求和得到的总电压VT等于四个信号电压的线性和加上四个噪声电压的RSS值,即:

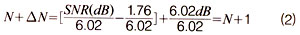

由于VS1=VS2=VS3=VS4,等效于信号被放大了四倍,而ADC的噪声(RMS值)只放大了两倍,从而使信噪比增大两倍,即增加6.02 dB。因此,四路信号求和所获得的6.02 dB增量(?SNR)使有效分辨率提升了1bit。因为SNR(dB)=6.02N+1.76,N为位数,所以,

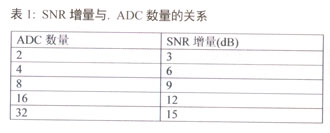

表1 中示出了多个ADC输出加和所获得的SNR增量。从简单性考虑,四个ADC加和是显然的选择。某些重要应用也会考虑更多的ADC加和,但应取决于其它系统指标要求(包括成本)和可提供的印制电路板(PCB)尺寸。

14 bit ADC理想的SNR为(6.02 × 14) + 1.76 = 86.04 dB。然而,AD6645的技术资料中提供的SNR的典型值仅为74 dB,所以其ENOB仅为12 bit。

因此,四路转换器输出求和可以补偿额外的1 bit分辨率,加上原来系统级ENOB可到达13 bit(80 dB) 。

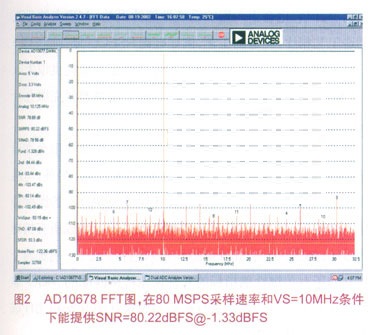

当然,这样的系统需要付出一些设计努力,以及一些系统原型设计、鉴定和测试开发的代价。但是,AD10678集成了4个AD6645,一个时钟分配系统,以及一个已配置好的复杂可编程逻辑器件(CPLD)以提供高速加法运算。现在可提供的AD10678以低成本和占用2.2 × 2.8英寸PCB面积的封装,通过测试完全达到规定技术指标。图2所示的快速傅立叶变换(FFT)结果证明了ADC的优良性能,在80 MSPS时钟和10 MHz模拟输入条件下能够提供80.22 dB SNR。

除了提高SNR,这种体系结构还提高了DC精度。四个ADC的失调和增益误差是不相关的,因此采用降低噪声一样的方法来降低系统失调和增益误差。但是在线性误差方面上没有改善,实际上无杂散动态范围(SFDR)取决于最差的ADC。

但是这种方案需要占用较大的PCB面积和4倍的功耗,但与以4倍采样速率工作的单ADC的输出平均方案相比,采用这种方法仍然具有优势。尽管以提高采样速率增加采样点数也会降低输入信号中的常模噪声。随着制造工艺的改进,新的设计使ADC的内核功耗进一步降低;另外可提供的4通道和8通道ADC的出现使多ADC系统更容易实现,并且减小了封装尺寸。例如,AD9259 4 通道14 bit, 50 MSPS ADC采用 48引线LFCSP (7 mm × 7 mm) 封装,其每通道功耗仅为100 mW。

虽然用提高输入电压的标准化做法来提高规定的SNR是可行的,但这会增加驱动放大器的设计压力,并且由于信号和噪声一起被放大,所以会降低系统SNR。加和体系结构的另一个微妙优点是,满度模拟输入不需要大于使用单ADC时的输入。

比较硬件和软件成本,信号平均的方法本身要比数字滤波有优势,但对于要提供经济有效的硬件处理和软件滤波的总体系统考虑所要求的数字滤波,软件常常使工作更容易。

ADC 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 12位串行A/D转换器的原理及应用开发(10-09)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 深入解析:模拟前端模/数转换器的三种类型 (11-26)