等价型PG逻辑及其在加法器设计中的应用

时间:11-28

来源:互联网

点击:

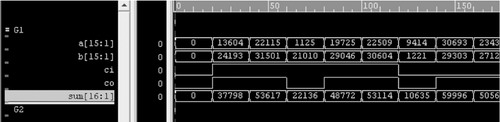

了如上所述的15位加法器的Verilog描述,并用ModelSim对其进行了仿真,对随机数进行相加,得到了正确的结果,说明在逻辑上该PG逻辑是正确的,如图8所示。其中a、b为两个15位的随机数,ci为随机的进位输入,co为进位输出,sum是最终的和(其最高位是co)。

图8 运用等价型PG逻辑设计的15位加法器的仿真波形

结语

本文根据现有PG逻辑计算公式,推导出了一种新的与之等价的逻辑表达式。将这一逻辑表达式运用到加法器设计中去,能够改变PG传播网络的结构,减少连线数目,降低布线复杂度,这样会更有利于后端的版图布线。但此方法会相应增大某些节点的负载,势必带来延迟的增加,因此需要精心设计晶体管尺寸或增加节点处的驱动能力,以使电路达到时序要求。

在今后的全加器设计中,可以根据具体情况灵活调整PG传播网络的结构,尽量使得布线与负载达到一定程度的平衡。

- 电源管理总线的结构与优势(11-19)

- 新型灌封式6A至12A DC-DC μModule稳压器系列(11-19)

- 用D/A转换器实现高精度可编程增益放大器(11-25)

- 低电压PLD/FPGA的供电设计(01-24)

- 基于FPGA的高精度数字电源(02-12)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)