全差分CMOS运算放大器的设计

摘 要:研究了一种全差分高增益、宽带宽CMOS运算跨导放大器(OTA)。 放大器采用三级折叠2级联结构,结合附加增益提高电路,大幅提高整个电路增益的同时获得较好的频率特性,采用0.35μm CMOS N 阱工艺设计。 HSPICE 模拟结果放大器的带宽为215 MHz(相位裕度62.2°),开环增益为103dB ,功耗仅为2.01mW。

关键词:运算跨导放大器(OTA);折叠-级联;增益提高;带宽

设计原理

一种采样频率为48kHz、过采样比为256的三阶三位Σ-ΔA/D调制器,设计中最关键部分就是积分器中的运算放大器。它不仅需要很高的增益来满足精度要求,还要有较大的单位增益带宽来满足过采样的速度要求,而这两个要求是互相制约、互为矛盾的。 实现宽带一般采用短沟器件、较大的偏置电流、单级设计;而实现高增益则一般采用长沟器件、较小的偏置电流、多级设计。

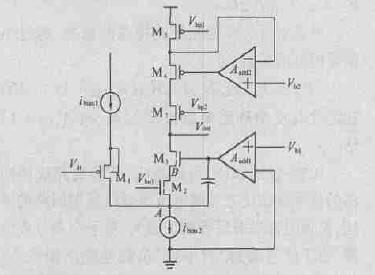

本文给出了一种新颖的全差分CMOS运算放大器的设计方法,主电路采用三级折叠-级联结构,并利用增益提高技术,在保持较好频率响应的前提下,使电路增益明显提高;且附加电路易于设计和实现,只增加较少的功耗和芯片面积。 基于此方法的电路结构如图1 所示,主电路采用三级折叠-级联结构,信号通路上附加增益级和M2及M3共同组成一个大的反馈环路;负载通路上附加增益级和M5 组成一个反馈环路。

图1 三级级联附带增益提高结构(半边电路)

增益的提高

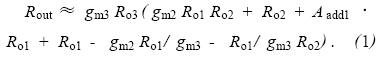

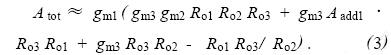

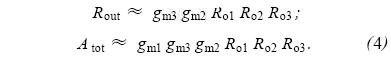

假设负载阻抗无限大,分析图1 的信号通路,并假设图1 中附加增益放大器是具有直流增益为Aadd1的理想增益级,忽略M2及M3 的体效应, 计算电路输出阻抗的小信号模型如图2 所示。 通过计算得到

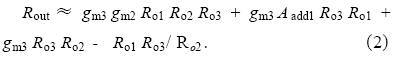

因设计时一般选择M2和M3尺寸相同,故式(1)可进一步简化为

低频本征增益

没有反馈环路时,M3 的栅极连接偏置电压, 其输出阻抗和低频本征增益分别为:

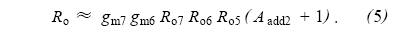

因gm3 Ro3 Ro2和Ro1 Ro3/ Ro2在同一个数量级,比较式(3)和(4)可以看出,本征增益大约提高gm1 gm3 A add1 Ro3 Ro1 。再来看看负载通路阻抗提高的情况。 通过小信号模型的分析,得

比之没有反馈环路前阻抗增加至少(Aadd2+1)倍。

图2 输出阻抗计算的小信号模型

比较式(2)和(5)可以看出,信号通路反馈回路的这种接法比之负载电流源通路反馈回路的接法,前者阻抗没有后者增加得大。 对于全差分放大器,由于信号通路"看不到"负载通路的极点,负载通路的附加放大器(Aadd2)可不考虑其对主电路频率特性的影响, 因此采用后者的接法以便以较小的Aadd2的值即可满足对负载通路阻抗的要求。

频率特性

设图1中未附加增益级的原主电路的主极点频率(即输出极点) 用ωo1表示, 第一个非主极点(即图中B 点所代表的极点) 频率用ωo2表示, 第二个非主极点(即图中A 点所代表的极点) 频率用ωo3表示;附加放大器A add1的单位增益频率用ωa1表示。

要想不影响原主电路的频率特性, 根据分析,图1中若将Aadd1附加放大器反馈至M2管( 同负载通路), 附加放大器设计需满足ωo2 <ωa1 < ωo3 ;本文给出的将Aadd1附加放大器反馈至M3 管这种接法, 附加放大器设计需满足ωo1 <ωa1 <ωo2 。

可以看出本文给出的设计Aadd1附加放大器要求的单位增益频率在一个较低的范围内, 因此其实现相对要简单,不必在增益和带宽之间进行艰难的折衷。

电路实现及模拟结果

图3即为本设计的全差分OTA。主电路采用PMOS 输入对管,三级折叠2级联。附加放大器采用简单的共源放大即可,由于不必在增益和带宽之间进行折衷,可采用较小的偏置电流以降低功耗,Aadd1附加放大器靠共源放大管用宽沟道管来增大其增益;在共源放大管前面增加二极管连接晶体管作电平转移, 使其不影响主电路的输出信号摆幅,突出的优点是实现简单,不需增加额外的偏置电路。 采用开关电容共模反馈电路以稳定高阻输出节点的直流电压;偏置电路采用一个主控电流源并利用电流镜产生一些偏置电流(图5中未画出偏置电路部分) 。 另外电路中增加MP1和MP2管,其作用是提高放大器的转换性能。

在高频下,精确测量全差分幅频及相频特性是很困难的,本文所有的模拟结果都是基于单端的,双端增益值应在测量值

- 高速差分ADC驱动放大器AD8137及其应用(01-17)

- 基于开关电容共模反馈理论分析(05-30)

- 基于Multisim的差分放大电路仿真分析(06-14)

- 差分放大器中的不匹配效应及消除方法(08-19)

- 全差分驱动器开启高速ADC的高性能应用之门(04-19)

- 平稳地远程传送高速模拟/数字转换数据(06-28)