一种0.18um 2.4GCMOS低噪声放大器的设计

时间:11-03

来源:互联网

点击:

3 软件仿真

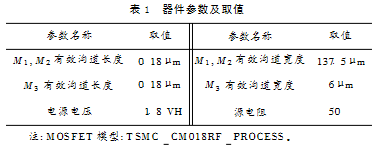

本文运用TSMC 0.18 μm CMOS工艺库,采用Agi-lent公司的ADS进行仿真,电路器件参数及取值如表1所示。

|

|

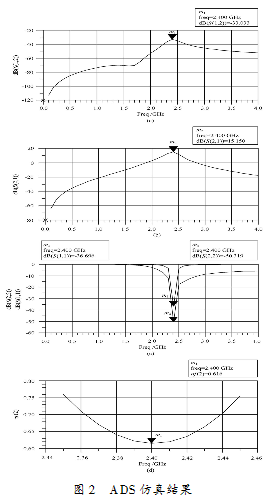

仿真如图2所示,在中心频率为2.4 G时,电路功率增益S21为15.15 dB,隔离度S12为-33.03 dB,输入与输出反射系数分别为-36.70 dB与-50.32 dB,噪声系数仅为0.62 dB。1.8 V时直流功耗为7.9 mW。这些指标能很好地满足RF电路对低噪声放大器的设计要求。

4 结 语

从仿真结果可以看出,在共源共栅结构的基础上同时采用级间匹配、π型网络以及电压并联负反馈的低噪声放大器输入输出匹配良好,这反映在电路的噪声系数达到了很好的水平,增益比不采用级间匹配和电压并联负反馈时增加了约2 dB左右,达到设计要求。

采用此结构设计的深亚微米CMOS射频低噪声放大器,由于设计中充分考虑了功耗、增益、噪声系数、线性度及品质因数之间的折衷关系,所以达到的设计性能优良。在深亚微米水平上实现低噪声放大器的设计具有重要意义,在大规模数模混合集成电路中很有应用潜力。

|

|

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- CMOS求和比较器在PWM开关电源控制中的应用(11-27)

- 如何将CMOS LDO应用于便携式产品中(01-15)

- 2.5 Gb/s 0.35μmCMOS光接收机前置放大器设计(01-22)

- 用于下一代移动电话的电源管理划分(08-28)

- 不同电源供电的器件间的桥接(04-27)