音频功率放大器的CMOS电路设计

时间:04-18

来源:互联网

点击:

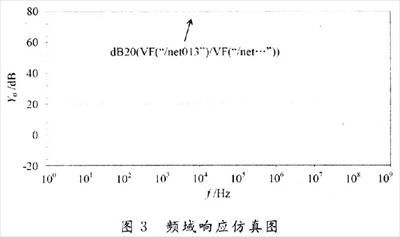

仿真性能参数如表1所示。用Cadence Spectre进行仿真。使用了华润尚华0.5μm的N阱CMOS工艺模型,模拟环境是VDD=5 V,T=27 ℃典型条件。在5 V单电源下驱动8 Ω负载。对于1 kHz,4 V峰一峰值的正弦波激励,仿真得到负载上的电压基波幅度为3.9l V。此时电源消耗的平均功率为3.15 W,功率放大器的效率为60.7%。总谐波失真为0.098%。总体上THD和效率随输入电压变大而增加。放大器频域响应如图3所示。

3 结语

该设计的AB类输出功率放大器电路,采用折叠式共源共栅结构,功率管推挽式输出,同时利用外部电流源供电,采用低压共源共栅电流镜结构的偏置电路。仿真结构表明该运放具有高增益,低输入失调电压,低THD等特点,同时具有良好的频率特性,较低的静态功耗,满足一块高性能的AB类音频功放芯片的要求。

- 音频系统应用中的“POP”噪声以其常用解决方法(12-01)

- 20位单片音频数模转换器PCM63P (01-22)

- TDA2030音频功率放大电路(02-07)

- 适合音频扩展基座设计的完整音频解决方案(06-03)

- 基于DPPC2006的数字音频功率放大器(05-05)

- 新型人机对话接口与音频数据转换器技术及选用(05-23)