一种单端10-bit SAR ADC IP核的设计

时间:09-11

来源:互联网

点击:

2 版图设计与系统仿真

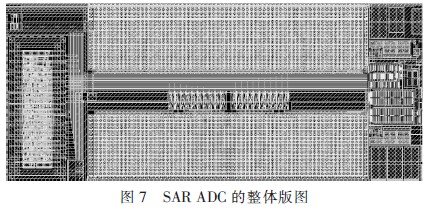

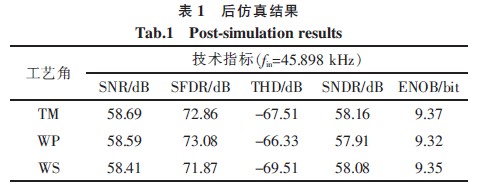

本设计基于Cadence Virtuoso版图编辑工具对SAR ADC进行布局布线和版图绘制。电容阵列采用MIM(metal-insulator-metal)电容,提高了工艺兼容性,减小了成本。在版图布局方面,电容阵列采用对称的布局方式进行布局,有效地减小了电容匹配误差。由于本文的逐次逼近寄存器及控制电路是采用verilog编码,并通过Encounter工具生成的数字电路,因此本文将数字电路和模拟电路分开布局,并用电地环进行隔离,以防止相互干扰。电路版图如图7所示,芯片版图面积约为800μmx340μm。最后利用Assura软件从版图生成了带寄生参数的网表,并进行了后仿真,以验证电容不匹配及寄生参数等对电路的精度、速度的影响。在采样速度为1-MS/s,信号频率为50 kHz的情况下,后仿真的3种工艺角结果如表1所示。从表1中可以看出,ADC的有效位数为9.3 bit左右,基本达到预期目标,可以正常工作。

3 结论

文中设计了一种单端10-bit SAR ADC IP核,分析了整个系统的主框架和数模转换电路(DAC)以及比较器。采用XFAB 0.35μm CMOS工艺,利用Cadence Spectre软件,对系统进行了仿真。仿真结果表明在电源电压3.3 V,输入电压范围0~1.5 V,采样速率为1 MHz,输入信号频率50 kHz的情况下,测得有效位数ENOB为9.37 bit,SNR为58.69 dB,SFDR为72.86 dB,THD为67.51 dB,SNDR为58.16 dB,功耗仅为

4 mW。满足设计需求,可以应用于单端输入信号电路中。

- 适用于SAR ADC的CMOS比较器的设计(01-02)

- 采用差分PulSAR ADC AD7982转换单端信号(10-01)

- 最佳的解决方案带来高精度(01-22)

- 精密SAR模数转换器的前端放大器和RC滤波器设计(02-11)

- 低功耗 ADC(04-06)

- 逐次逼近型(SAR)模数转换器在马达控制中的应用(06-15)