使用次级端同步整流器电路来降低功率损耗

平(大约1~2V)。该信息用来确定同步整流器栅极针对下一个开关周期的关断时间。为什么能够使用这个功能,原因是LLC拓扑的高侧和低侧开关占空比是对称的,在稳定状态下,开关频率不会有大的变化。控制导通的定时使用了MOSFET的体二极管,MOSFET先导通,然后断开。

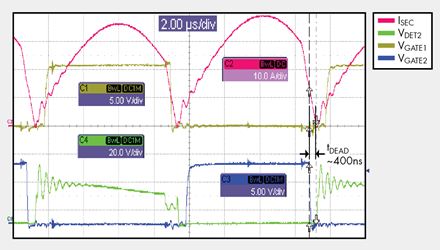

图7所示为这种控制方式。在过程开始时获取信息作为控制MOSFET关断的方法,这种方法使GATE较早关断,以防止由于某些原因而造成MOSFET晚关断。在MOSFET导通且受到噪声和连线的一些干扰时,这种方式比直接检测VDET上微小负电压的方式更加稳定。由于电流低至0A,tDEAD的周期(从GATE关断的定时到IDS的定时)将变长,减低同步整流器的活动性可以改善能效。

图7. 同步整流器的VDS波形

4. 使用LLC谐振转换器初级端栅极信号的同步控制

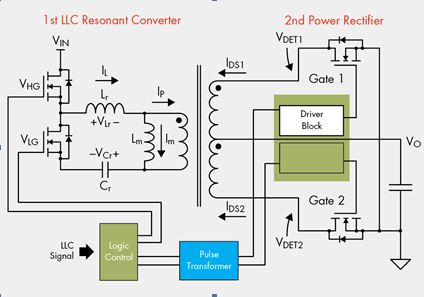

使用LLC谐振转换器初级端栅极信号的同步控制是最直接的控制方法。使用由初级高侧和低侧信号计算而来的GATE信号,并将结果提供给次级端,控制相应的次级端MOSFET的导通和关断。如图8所示,处理高侧和低侧的额外信号后,使用逻辑电路发送信号来控制次级端的MOSFET。注意,VHG和VLG的信号不能直接从计算导出,最有效的方法是使用LLC的信号来生成VHG和VLG信号,控制初级端的MOSFET。因为在大多数情况下,相应的次级端MOSFET需要早于初级端MOSFET关断,原始的LLC控制信号不能直接驱动MOSFET,必须发送一个新信号。

图8. 使用初级端LLC信号控制同步整流器电路

使用这种检测方法时必须满足两点要求:

A. 当在II区域中使用LLC时,由于可能出现谐振电流IL低于磁性电流IM,这会使IP为零并且造成初级端和次级端的去耦合。去耦合的主要条件是次级端二极管关断。所以,如果要改变同步整流器电路,需要在这一时间间隔内关断MOSFET。我们无法通过监测初级端LLC控制的信号来了解该现象何时出现,所以必须添加功能,早些关断SR,以阻止电流反向。

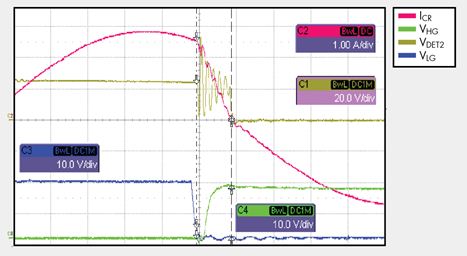

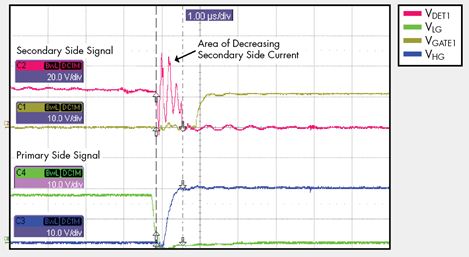

B. 当LLC系统工作于I区域时,从图9我们能够找出初级端GATE信号与次级端电流的关系。当低侧MOSFET关断时,次级端的相应电流还没有降到零,所以,虽然次级端没有出现相位立即改变的情况,但会发生相位置换的情况。工作于I区域的现象和相位置换时间的长度将会伴随过载的交换。因此,当使用初级端信号来控制同步整流器时,设计人员应增加功能,以推迟同步整流(SR)的导通和关断。这样会确保这种情况不会发生并且能够防止同步整流器受到初级端谐振电流的损坏。图10所示为正常工作的同步整流器波形。

图9. 次级端和初级端LLC信号的绕组电压波形

图10. 同步整流器波形和初级端LLC信号

III.结论

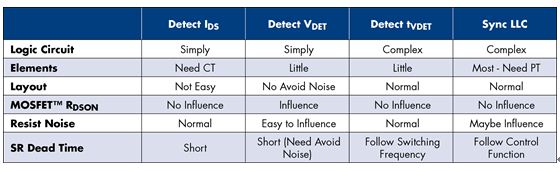

最后,表1给出了四种检测方法。从逻辑上讲,当MOSFET导通时,就控制而言,检测电流会比检测VDET容易。最复杂的方法是与LLC信号同步,这要求增加功能,以改善I区域和II区域的情况。检测电流需要使用电流互感器(CT),而使用初级端LLC的信号则需要电压互感器(PT)。因此,各种因素更加难以控制。在布局设计过程中,设计人员在确定电流互感器的电流检测方法以及MOSFET非常精确的RDSON电压时必需非常仔细。因为检测到的RDSON电压大约为1mV至10mV,所以更易受到干扰。采用通过PT发送同步信号的初级端LLC信号方式,要求设计人员考虑噪声问题。

如果同步整流器死区时间受到布局和已降低噪声的影响,检测RDSON电压的方法可以使得变化最小。由于交换频率的差异,检测VDET所需的时间将改变同步整流器的死区时间。从安全方面考虑,该功能时间是最长的。与LLC信号同步的方法将根据I区域相位移动的改善程度来确定同步整流器的死区时间。高效设计的最终考虑因素表明同步整流器的死区时间越短,其工作效率越高。因为增加电流互感器来检测电流会增加损耗,其效率将会低于检测VDET时间的方法。因此,在设计过程中,我们可以选择合适的检测和控制功效的方法。

表1. 次级端绕组电压波形和初级端LLC信号

- 计算机电源“白金”化(06-08)

- 如何设计一个合适的系统电源(上)(11-20)

- 什么是MOSFET(11-26)

- 包含热模型的新型MOSFET PSPICE模型 (11-26)

- 用IGBT代替MOSFET的可行性分析(11-27)

- MOSFET的谐极驱动(11-27)