使用次级端同步整流器电路来降低功率损耗

I. 前言:半桥LLC转换器

为了获得更高的功效,与200W到800W双管正激转换器相比,LLC谐振转换器的初级端MOSFET能够轻易达到零电压开关(ZVS),以期节省能量,并且获得更高的效率。此外,LLC谐振转换器使用独特的部件,能够省略次级端的储能电感,优于双管正激转换器的方案,并减小在印刷电路板上的占位面积。由于LLC谐振转换器的特性,将会以临界导通模式(BCM)或不连续模式(DCM)处理次级端电流,电流峰值将会大于双管正激转换器的电流峰值。下面将介绍几种使用不同的检测信号来控制MOSFET导通和关断的方法。

II. 同步整流器控制方法的分析

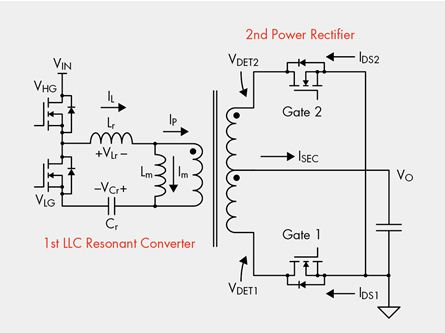

在LLC谐振转换器控制次级端整流器时,尤其是在关断的过程中,MOSFET导通和关断的控制定时是非常重要的。我们可以使用检测LLC谐振转换器初级端或次级端的电流或电压信号的方式,来确定MOSFET导通的区域。图1为LLC转换器的同步整流电路图。我们使用所示的电压和电流符号,介绍四种在次级端同步整流器关断过程中控制MOSFET的方法。

图1. LLC转换器的同步整流器电路图

1. 检测次级端电流(IDS1和IDS2)

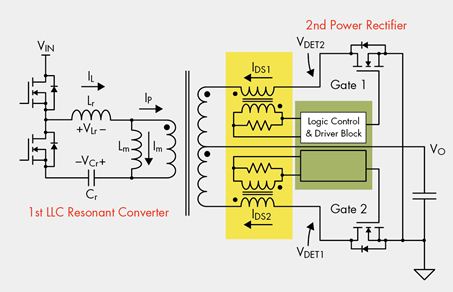

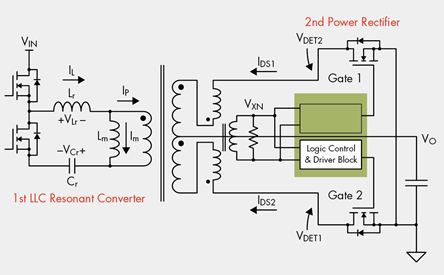

通过检测MOSFET的电流,可利用次级端同步整流器来控制MOSFET导通和关断的时间,如图2和3所示。由于需要检测IDS1和IDS2,需要增加一个电流互感器(Current Transformer, CT),从MOSFET信号中获取控制信息。与初级端电流相比,次级端电流要大些,所以电流互感器的匝数比很大。最后,设计人员可以使用电阻将分离的电流信号变换成电压信号,并将其发送至逻辑电路来控制MOSFET器件。

图2所示为使用两个电流互感器来检测电流信号,图3所示为使用一个电流互感器来检测电流信号的情况,在这个设计中,电路布局受到更多的限制,但是省去了一个电流互感器并且节省了线路板面积。

图2. 使用双电流互感器检测同步整流器电流

图3. 使用单一电流互感器检测同步整流器电流

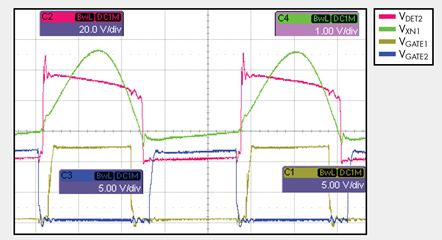

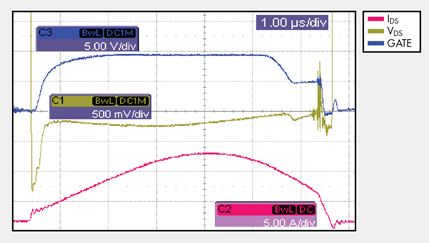

图4所示为每个相位的情况,该相位使用由电流互感器的检测电流转换而来的电压,以便控制MOSFET波形和GATE信号。设定的电平用作控制MOSFET导通和关断的基点。图5所示为一个电流互感器检测到电流后的两个相位,转换成电压以确定MOSFET导通和关断的波形。我们观察到电流互感器检测到的波形是交流信号VXN,并且具有一个不同的输出负载波形。在轻负载下,次级端电流集中在开关周期的终端,所以,控制MOSFET的GATE打开信号的时间会更短。如果输出电流继续降低,电流互感器检测到的电流将会减小,我们可以使用检测到的电平来确定在轻负载或无负载情况下关断同步整流器的时间。

图4. 双电流互感器控制同步整流器的波形

图5. 单一电流互感器控制同步整流器的波形

虽然使用电流互感器检测电流信号能够控制MOSFET导通和关断的时间,但还是存在不足。通过监测流过电流互感器次级端的电流来检测信号,会少许增大电流互感器的电流损耗,略微降低SR的效率。如果是这样,在发生最轻微的过负载时必须关断同步整流器的功能,设计人员必需在两个电路相位反转和交替时仔细监测电流。

2. 检测次级端同步整流器电压VDET

使用电流互感器检测次级端电流,可以方便地控制MOSFET,但为了避免电流互感器上的损耗,可以使用另一种检测方法。为此,在检测MOSFET导通时,利用RDSON上的电压来揭示MOSFET电流的直接比率。这样在MOSFET导通时检测了电压,并且提供了一种控制关断时间的方法。MOSFET导通定时使用了跨越MOSFET的体二极管。当次级端电流相位转换时,电流通过MOSFET,使其关断。使用这些条件来控制MOSFET的导通定时,MOSFET上的电压将会降低二极管的正向电压VF。如图6所示,当IDS开始通过MOSFET的体二极管时,MOSFET上的电压VDET为负,触发发出GATE信号来导通MOSFET。在GATE导通时,可以观察到VDET下降,电压为RDSON*IDS。

图6. 同步整流器的VDS波形

该检测方法可与使用电流互感器检测电流的方法相媲美,防止电流互感器之间和电流互感器上的能量损失,并精确地控制电流互感器的使用。这种方法最适合LLC次级端同步整流器。重要的是保证检测VDET 信号到控制电路之间的间隔不能太长,可能由于线路内电感的寄生效应造成信号的失真,此外,需要控制的信号会受到干扰。选择最低的MOSFET RDSON和最小的过载输出是控制MOSFET关断定时的简便方法。

3. 检测次级端同步整流器的导通周期

在MOSFET导通时,可以使用与检测V?DS相同的方法来检测VDET电压。通过检测VDS导通时间,并且在MOSFET导通后VDET处于接近0V的低电压下,可以测量同步整流器的导通时间(tDETL),在这段时间内,DETL低于低电

- 计算机电源“白金”化(06-08)

- 如何设计一个合适的系统电源(上)(11-20)

- 什么是MOSFET(11-26)

- 包含热模型的新型MOSFET PSPICE模型 (11-26)

- 用IGBT代替MOSFET的可行性分析(11-27)

- MOSFET的谐极驱动(11-27)