锁相环时钟相位调整电路

时间:06-26

来源:互联网

点击:

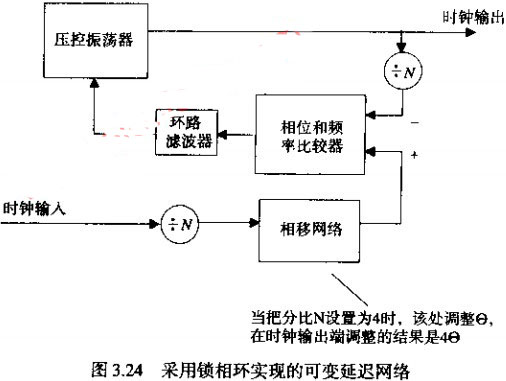

图3.24给出了CADILLAC时钟相位调整电路的框图。对于大规模生产测试,可能值得构造这样的电路。对于普通的实验测试,则太麻烦了。

电路将总线时钟进行N分频,然后通过一个-频率比较器把它与一个同样经过N分频的本地振荡器相比较。电路的频率锁定在与总线时钟相同的频率上,但是相位由相移网络决定。

因为相位锁定的频率是时钟振荡器频率的I/N,因此如果在相移网络中加入Y度的相移调产生一个很小的相移。由变容二极管控制的RC移相器可以很方便地做到这一点。

这个电路的相位调整范围可以超过正负180度。当系统的时钟较高,并且经过分频将信号频率降低来产生本地控制信号时,这种较大的相位调整非常有用。大的相位调整对调试允许多个时钟周期抖动的导步电路也很有用,例如通信中的T3同步器和FIFO电路等。

VCO的稳定性和相位检测网络的噪声不敏感特性,在这个电路里面至关重要。如果并不擅长模拟电路的设计,最好在制作这个电路时寻求些帮助。

- 全数字锁相环的设计及分析(03-01)

- 一种大电压输出摆幅低电流失配电荷泵的设计(04-22)

- 锁相环同步检波技术及在视频检波中的应用(05-20)

- 一种基于CMOS工艺的电荷泵锁相环芯片的设计(05-21)

- 基于锁相环的频率合成电路设计(07-30)

- 锁相环相位噪声与环路带宽的关系分析(08-04)