SAR ADC运放选择策略

路中的相关数值, 采集时间和RC滤波器时间常数之间的比率 (k) 取决于ADC的分辨率。最后,选择具备足够增益带宽的运算放大器来驱动该RC电路,而且所选的运算放大器应具有适当的调整时间。对许多不同SAR转换器的应用来说,该设计驱动电路的程序非常稳健而有效。然而,有时候作为能够改善性能系统的RC滤波器的一些优化措施而言,这仅仅是一个开始。

在优化ADS8361前端的输入RC滤波器之前,需要确定有关的工作条件:输入时钟频率为9.9968MHz,采样频率为199.936kSps;由这两个数值得到ADC转换时间为1.6ms,采样时间为3.4ms。因此,该转换器需要12个时间常数的外部RC滤波器来相应的采集时间匹配。这种条件可将RC电路的带宽设置为:

其中:k =12,由此可以实现562kHz的带宽。

低噪声系统可以采用尽可能高的带宽,但是,也不要把带宽设置得过高。因为带宽越高,其所允许的噪声也就越高,所以应在 RC 设定时间和该带宽之间取得一个平衡值。为了确定 RC 滤波器的最佳值,我们使用一个低输出阻抗的信号源。注意,最终计算结果应包括信号源的输出阻抗。在该示例中,该阻抗为 20Ω。从这些测量结果中发现,当 k = 7 时,可获得最佳 THD 值;而当 k = 6 时,可获得最佳的 SFDR 值。并且,k 值越小,RC 滤波器的带宽也就越低,从而降低了噪声。然而,当 k 值变小时,性能也随之降低。出现这种情况是因为时间常数太大,而且它不能对采样电容器上的输入电压进行相应的设置,从而导致测量误差的出现。

结论

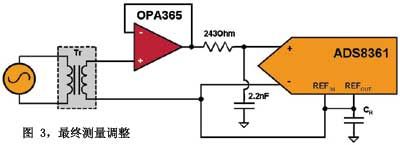

为了完成信号链的最终性能评估,选用当k = 6.36或截止频率 = 298kHz 时的RC滤波器。在这种前提下,我们采用一只2.2nF的COG型电容器和一只243Ω的电阻。

当采用ADC最高的采样速度时,采集时间为 400ns。采用上述相同标准(k = 6.36)时,一阶滤波器的有效噪声带宽为 4MHz。当采集时间由 400ns 延长至 3.4ms 时,有效噪声带宽则下降为 562kHz。图 3为最终调整图。

- 信号链的集成与去集成 (04-21)

- 信号链基础知识 RS-485:总线电流要求与收发器驱动能力(04-27)

- 高精度单向电流检测放大器电路设计(11-01)

- 更高的集成度、更低的成本需要更深入的系统理解(01-30)

- 信号链基础知识57:工业远距离通信使用的RS-232至RS-485转换器(01-23)

- 信号链基础知识#70:模拟正交调制器失衡的数字校正(01-20)