基于Cadence的COMS低噪声放大器设计

结合CHRT 0.35μm RF CMOS工艺的PDK,可以很方便地生成电路的元器件版图输出,接着完成必要的电路连线,便可以得到电路的版图结果。

电路实现版图设计之后还需要完成物理验证。

此次采用的验证工具是IC 5.1中自带的divA。除此之外,也可以采用Cadence公司的ASSura,或者Mentor Grahphics公司的Calibre。物理验证的过程包括设计规则检查(DRC)、版图原理图对比(LVS)以及寄生参数提取(Extract)三个步骤。

在版图编辑器(Layout XL Edit)的Verify菜单当中,可以找到DRC,LVS,Extract对应的选项;在完成了必要的参数设置之后,便可以完成电路的物理验证。在做完寄生参数提取之后,便可以利用包含寄生参数的电路完成电路后仿真(Post-layout simulation),从而得到与实际电路性能更为接近的各项仿真结果。

(3)实验结果。在完成最终电路的调试后,得到了各项仿真结果。

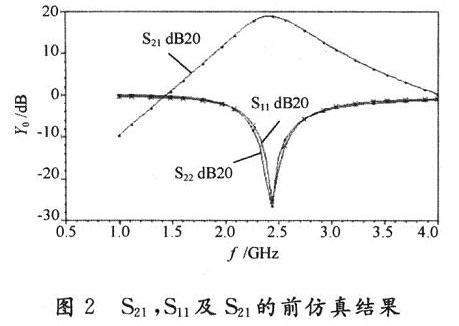

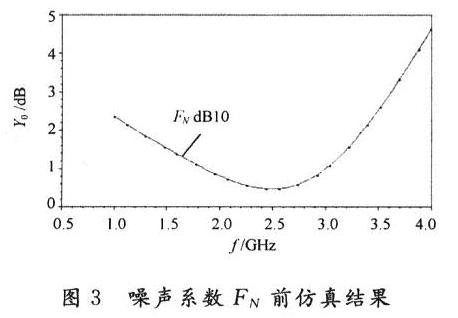

图2、图3分别是用电路原理图仿真(即前仿)得到的S参数以及噪声系数FN的实验结果。

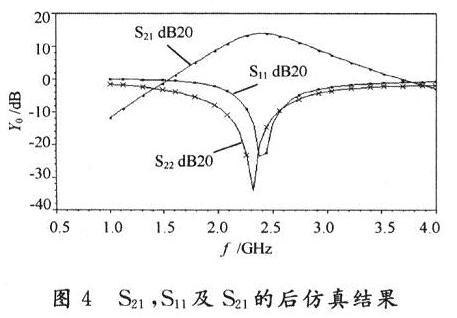

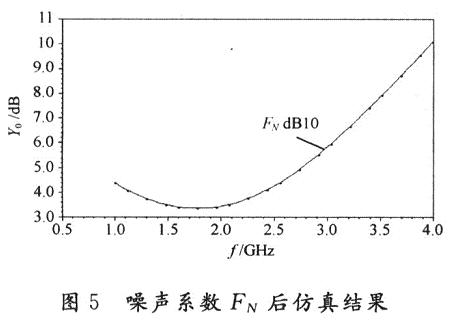

图4、图5是完成版图之后,考虑寄生参数的电路后仿真结果。图4是S参数的后仿真结果。由S11,S22的曲线可知,在2.4 GHz的中心频率附近,S11,S22<-10 dB。可见,输入、输出电路均有比较好的匹配。图5是噪声系数FN的后仿真结果。图6为电路版图。

与电路的前仿结果相比,后仿真的噪声系数有一定的上升,这说明电路中的寄生参数会使电路的噪声性能恶化。

3 结 语

结合一个具体的低噪声放大器(LNA)设计实例,采用CHRT的0.35μm RFCMOS工艺,在EDA软件IC 5.1设计环境中设计了一个2.4 GHz的低噪声放大器。设计过程中完成了电路原理图仿真、版图设计以及后仿真。实验结果表明该低噪声放大器具有较好的电路性能。结合设计过程,还介绍了如何运用Cadence软件对CMOS低噪声放大器进行电路设计和仿真。

- 利用Cadence设计COMS低噪声放大器(06-11)

- 基于ADS的通信设备低噪声放大器改进设计与仿真(04-09)

- 航天GPS接收机的低噪声放大器设计(05-10)

- X波段低噪声放大器设计分析(08-01)

- 一款超低噪声S频段放大器设计(09-13)

- 低噪声放大器设计(09-11)