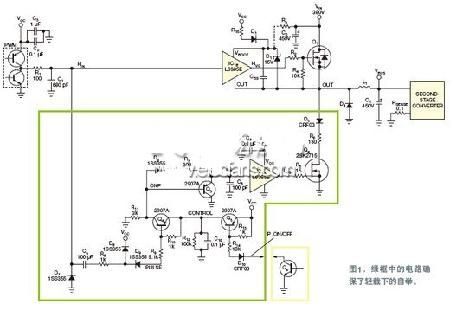

轻载下自举工作的电路设计

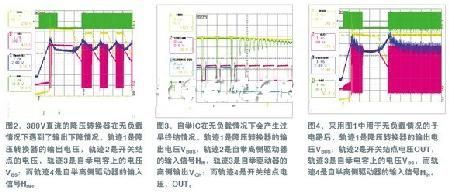

图1中,绿框中是增加的电路,它解决了总线电压信号的电压下跌问题。图2中的波形表示了在降压转换器IC1B中如何出现这一问题,在无负载时,其输出电压VBUS以一个固定速率跌至调节点以下。通过图2中的其它轨迹可以得到结论,当自举电压低于其8.66V阈值时,就会发生VBUS的下跌(轨迹3),从而致使降压转换器开关停止动作。当总线电压接近于输入电压时,这种情况更加严重。

在DCM(非连续导通模式)的续流工作期间,输出信号(图3,轨迹4)倾向于在电感L1完成放电后,安定于总线电压。这一动作可阻止自举电容CBS的充电,最终会使图2中的自举电压降到8.66V以下。因此,降压转换器就停止了工作。

图1绿框中的电路可以解决这个问题。它开始时先将输入信号分接到自举的高侧驱动器上,产生一个反相并延迟的短脉冲,用于控制Q2。一旦Q2被激活后,就强制输出信号立即为低,从而为CBS提供了一个充电的机会。R8、R9、R10、R11和C9 设定了Q2的导通周期。这个周期不得超过PWM(脉冲宽度调制)信号的死区时间。如果Q2的导通时间过长,则转换器的效率会下降,或者CBS可能无法充足电。Q2充电不足会影响多个元件值和工作参数,如Q2的导通时间,你可能必须凭经验调节延迟时间,以适应于这些效应。图1中的值在70 kHz的开关频率下,为Q2提供了1 μs的导通时间,以及450 ns的延迟时间。

Q5网络是可选的。它的作用是,当不需要将P_ON/off信号连接至集电极开路的Q6时,禁止Q2 的工作。IC1A的下半部分驱动Q2。必须通过试验来选择R6的值。如果选择的电阻值太低,则Q2激活时会产生较大的电流脉冲。另一方面,过高的电阻值则会使CBS充电不足。

电阻R7 与电容C8 控制着自举高侧驱动器的输入信号下降沿直到IC1A的LVG(低压)脉冲上升沿之间的延迟时间。图4显示在增加电路后,同一转换器的波形。此时,VBUS(轨迹1)保持稳定,而降压稳压器的输出信号连续地开关,没有了图2中波形所显示的开关间隙。

- 同步降压转换器电路设计基础(01-01)

- 电路设计基础知识--变压器(01-29)

- 不连续模式反激变换器的基本原理和电路设计(01-05)

- 牛奶成份检测仪光强检测电路设计原理(11-05)

- WCDMA分布式基站低噪声放大器电路设计(09-12)

- 基于AD7543和FPGA的数/模转换电路设计(10-19)