一种雷达多目标模拟器的主控DSP的软件设计和实现

摘 要 阐述了雷达多目标模拟器的设计,给出了一种可实时模拟多批目标回波的雷达信号模拟器的实现方案,重点介绍了该模拟器主控DSP软件设计思想及其实现,对整个系统工作性能做了简要分析。

关键词 DSP,SHARC,雷达信号模拟

Design and Implementation of Software for the DSP of A Radar Multi-Target Simulator

Li Weijiang Chen He Han Yueqiu

(Department of Electronic Engineering,School of Information Science and Technology,Beijing Institute of Technology,Beijing 100081)

Abstract The paper briefly presented the design of A Radar Multi-Target Simulator. At the same time, the design and realization of the radar signal simulator which can simulate multiple targets are introduced in detail. In this paper, the DSP software scheme and it’s realization of the radar signal simulator are presented mainly . It also made a simple analysis to the system’s performance.

Keywords DSP, SHARC, Radar Multi -Target Simulator

1 引 言

随着军事技术和信息技术的飞速发展,对雷达的性能提出了越来越高的要求。同时,缩短雷达系统设计、调试、联调和外场实验周期显得极为重要。而现代雷达系统面临的严重挑战是雷达工作环境的恶劣,要求在强杂波中检测目标和提取目标参数。因此,在雷达设计和分析中必然需要考虑大量非线性因素和随机因素, 而由于环境、配套服务、成本等诸多因素的影响,在现代雷达系统的设计、试验、训练过程中, 不可能总是采用真实目标。在这种情况下,雷达信号模拟得到了普遍重视。ADSP-2106x SHARC(Super Harvard Architecture Computer,超级哈佛结构计算机)是美国Analog Device公司生产的高性能的32位通用数字信号处理器(DSP)[1]。它具有很强的数据处理能力和与外部进行数据交换的能力,适于高速实时运算,广泛应用于通用数字信号处理、通信、雷达和声纳、图像处理、医学电子、高速控制等领域。

本文对一种基于ADSP-2106x SHARC的雷达多目标视频回波信号模拟器的方案作了简要介绍,该模拟器结合某型雷达的调试、性能评估等要求,采用PC上位机加基于DSP的目标模拟板等系统组合的方法实现。目标模拟板根据通过串口传来的由PC界面设置的目标信息和雷达参数等数据进行实时运算和调度,依次实时地产生相应的多目标雷达视频信号。其中主控DSP是整个系统的核心,其软件设计的思想和实现是本文介绍的重点。

2 多目标模拟器的系统构成

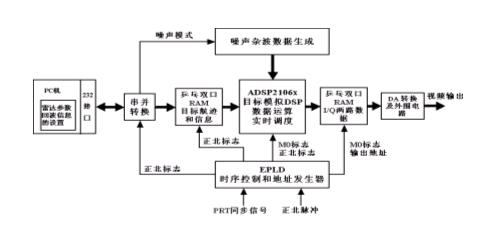

图1所示为雷达多目标模拟器的结构框图。

该系统主要由上位机和目标模拟器处理板两部分组成,PC机负责产生雷达参数、目标信息和航迹数据,可根据不同工作状态和不同运动形式进行仿真运算,将运算得到的目标航迹和状态数据以文件的形式存储起来,供实际模拟时调用。该雷达模拟器系统能模拟径向运动、切向运动、曲线运动目标,不同运动方式可通过PC界面设置进行选择,系统自动调用相应的信息数据。PC机与目标模拟板进行串口通信,天线每次扫描经过正北时目标模拟板向PC机发送数据传送请求一次,PC机接到数据传送请求后,通过RS-232接口或RS-485接口向模拟板发送下一次天线扫描周期的目标批数和信号波形码以及各批目标的方位、距离、信噪比、多普勒频率等参数。

目标模拟板主要由串并转换、噪声产生、数据运算调度、时序控制和地址产生、DA转换及其外围电路等五个部分组成:串并转换模块接收串口来的数据转换成并行数据写入乒乓双口RAM,并向噪声产生模块发送三位噪声模式码;噪声杂波数据生成模块由专用芯片(FPGA)实现,其接受上位机传来的噪声码从而可生成均匀分布、高斯分布、指数分布、瑞利分布四种随机数之一;时序控制和地址产生模块由EPLD来实现,其接收来自雷达信号处理机的正北脉冲和PRT同步信号,自行产生12位天线方位增量码、各模块所需的控制信号和输出地址;ADSP2106x是模拟板的核心,其读取乒乓双口RAM中的目标航迹和状态信息、FPGA中的噪声、来自EPLD的方位码,并通过运算、处理和调度实时完成雷达波形的产生、多普勒信息的调制、噪声杂波的叠加,并根据目标的距离延时依次将I、Q两路回波和噪声数据分别写入两个乒乓双口RAM,DSP通过其外部总线地址空间的合理分配实现与RAM、FPGA和其它外设的无缝连接(DSP外总线地址空间分配如图2所示); 最后在正确的时序控制下经高速DA转换、滤波、放大后形成I、

- 新型雷达发射机控制台显示控制技术的研究(07-15)

- 雷达天线电源故障检测电路的设计(01-27)

- 基于Simulink技术的噪声调幅干扰仿真(03-08)

- 毫米波雷达前端系统设计(05-03)

- 基于PCI总线的雷达视频高速数据采集接口设计(10-16)

- 基于Matlab的雷达系统仿真软件包设计与实现(09-16)