高频条件下IGBT驱动电路的设计与仿真

引言

绝缘门极双极型晶体管是复合了功率场效应管和电力晶体管的优点而产生的一种新型复合器件,具有输入阻抗高、工作速度快、热稳定性好、驱动电路简单、饱和压降低、耐压高和承受电流大等优点,因此现今应用相当广泛。但是IGBT良好特性的发挥往往因其栅极驱动电路设计上的不合理,制约着IGBT的推广及应用。本文分析了IGBT对其栅极驱动电路的要求,设计了一种适用于高频条件下小功率电路可靠稳定的分立式IGBT驱动电路。

1 IGBT驱动电路的基本要求

IGBT的驱动电路是IGBT与控制电路之间的接口,实现对控制信号的隔离、放大和保护,驱动电路对IGBT的正常工作及其保护起着非常重要的作用,门极电路的正偏压uGS,负偏压-uGS和门极电阻Rc的大小,对IGBT的通态电压、开关、开关损耗、承受短路能力参数有不同的程度的影响,因此驱动电路设计对IGBT的动态和静态性能都有重要影响,对驱动电路提出以下要求:

①动态驱动能力强,能为栅极驱动电压脉冲提供充分大上升率和下降率,以减小开通和关断损耗。但是,由于主电路中存在分布电感及滤波电容的串联电感,随着IGBT的高速开通与关断将在电路中产生高频幅值很高而宽度很窄的尖峰电压Ldi/dt,该尖峰电压应用常规的过电压吸收电路是吸收不掉的,因而有可能造成IGBT自身或电路中其他元件过电压击穿而损坏。所以,主电路应尽可能使用短引线或双绞线降低分布电感的影响,而且IGBT开关时间也不能过短,其值应根据所有元件及IGBT自身的承受du/dt的能力综合考虑。

②能向IGBT提供适当的正向栅极电压,IGBT导通后的管压降与所加栅源电压有关,在集射极电流一定的情况下,uGE越高,uCE就越低,器件的导通损耗就越小,这有利于提高开关效率。但是,uGE并非越高越好,一般不允许超过20V,原因是一旦发生过流或短路,栅压越高,则电流幅值越高,IGBT损坏的可能性就越大。通常取15V为宜。

③能向IGBT提供适当的反向栅极电压。IGBT栅射极施加的反向偏压有利于其快速关断,但-uGE反向偏压受IGBT栅射极之间反向最大耐压的限制,过大的反向电压会造成IGBT栅射极的反向击穿,所以-UGE应取合适的值,一般为-2V~-15V。

④有足够的输入输出电隔离能力。由于IGBT多用于高电压场合,而控制电路并不与高压电路有直接耦合,所以驱动电路应与整个控制电路在电位上有严格的隔离。但是,这种电隔离不应影响驱动信号的正常传输。

⑤具有栅极电压限幅能力,保护栅极不被击穿。IGBT栅极限电压一般为-20~+20V,超出此范围就可能破破环栅极。

⑥选择合适RG,IGBT驱动电路中的RG对工作性能有较大的影响,RG较大,有利于抑制IGBT的电流上升率及电压上升率,但会增加IGBT的开关时间和开关损耗,RG较小,会引起电流上升率增大,使IGBT误导通或损环。RG的具体数据与驱动电路的结构及IGBT的容量有关,一般在几欧一几十欧。

⑦IGBT的栅极驱动电路应尽可能的简单、实用,最好具有对驱动IGBT的完整保护能力及很强的抗干扰性能,而且输出阻抗应尽可能的低。

⑧由于栅极信号的高频变化,造成同一个系统多个IGBT的栅极驱动电路相互干扰。为防止干扰的出现,引线应采用绞线或同轴电缆屏蔽线,同时栅极驱动电路中IGBT模块栅射的引线也应尽可能的短。

2 实用型IGBT驱动电路

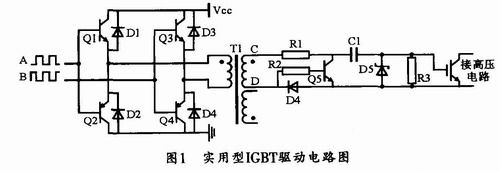

针对IGBT驱动电路的上述要求,在工程实践中提炼出一种简单实用的分立式IGBT驱动电路,其电路简图如图1所示,在电路简图中:Q1,Q3为NPN型三极管,Q2,Q4为PNP型三极管,D1~D4为保护二极管,二路PWM控制信号A,B为高电平或低电平,即A为高电平,B为低电平时,Q1、Q4导通,Q2、Q3关断,此时,Q1、Q4和T1原边绕组就形成通路,脉冲电压加在T1的原边,与原边同相位的次边得到开通驱动信号,与原边相反的次边得到关断驱动信号。这些部分的作用是将A、B信号推挽放大,并通过隔离变压器T1将驱动信号发生电路与高压电路隔离。

当开通驱动信号加在CD端时,在脉冲的上升沿,电容C1相当短路,通过门极电阻R1和加速电容C1向IGBT栅极提供较大电流,降低驱动脉冲的上升时间,最终IGBT因uGE上升至15V而导通。同时因为NPN三极管Q5的门极通过R2接至低电平,因此处于截止状态,对IGBT的导通没有影响;在脉冲平顶期,此时,IGBT的输入电容Cies已经满电,此时IGBT的G-E极之间相当于断开,变压器次边VCD保持高电平。当脉冲下降沿到来时,IGBT的输入电容在这段时间要反向放电,若放电速度太快,会引起极大的关断尖峰,造成IGBT的损坏;若放电速度太慢又会造成IGBT关断时间过长,形成较大的拖尾电流,造成关断损耗增加,降低效率。因此应该适当控制IGBT输入电容的放电速度。在图1的实用型驱动电路中,可以通过改变Q5的限流电阻R2和加速电容C1的值来实现Cies适当放电:当C1较大,R2较小时,一方面电容C1中储存的电量较大,另一方面,三极管Q5基极电流大使得发射极电流大,因此Cies的放电速度较大;当C1较小,R2较大时,Cies放电速度减小。又因为C1往往大于Cie-s,因此在输入电容Cies放电结束后,即IGBT关断后,C1上可能还残存少量电量,若没有适当的放电回路,这个电容经过几个脉冲周期后充满电荷,而失去加速作用,所以要求C1在每个周期上升沿到来时,电容上无存储电荷,因此在IGBT的G-E端并联电阻R3,给电容C1提供放电回路。D5为15V稳压管,防止驱动信号失控而造成的IGBT损坏。

- 用IGBT代替MOSFET的可行性分析(11-27)

- 以创新的IGBT技术、合理的器件选型和有效的系统手段优化变频器设计(01-09)

- 智能功率IGBT和MOSFET让汽车更加舒适环保(01-09)

- 单电源供电的IGBT驱动电路在铁路辅助电源系统中的应用(01-16)

- 面向汽车应用的IGBT功率模块浅谈(05-13)

- 使用栅极电阻控制IGBT的开关(04-13)