基于SoC的实时信号处理系统中存储系统的容错设计

时间:04-20

来源:eaw 作者:洪涛,韩承德,李栋

点击:

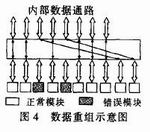

低纠错能力,数据重组逻辑也自动定向纠错码的数据通路。图4为数据重组示意图。

系统纠错容错能力分析

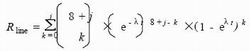

假设各个DDR颗粒之间发生错误的概率是互相独立的,设每个颗粒发生错误的概率恒定为λ,则每个DDR颗粒的可靠性符合泊松分布,其可靠性为Rm=e-λt。在Mem(i,j)系统中,每行的可靠性为

整个系统的可靠性为

重构前后系统可靠性的变化如图5所示。

由此,可以根据故障概率λ计算出系统的整体可靠性Rsystem,根据系统要求的可靠性可以反向计算出所需要的i,j,从而构建出完整的Mem(i,j)容错存储系统。

结论

针对SoC实时数字信号处理系统的特点,设计了一种新的具有自适应容错纠错能力的二级冗余存储体系结构。详细论述了系统在存储颗粒组织排列和信号连接方面对于纠错容错能力的支持、系统在逻辑设计上对纠错容错能力的支持等。新的存储系统容错方案可以有效地提高存储系统的可靠性,下一步的工作将集中在整个系统的低功耗优化方面。

- 统一功率格式降低SoC的功耗(05-28)

- 第三方IP:SoC设计的一种不稳固基础(09-15)

- 赛普拉斯智能照明解决方案支持欧司朗 DRAGON LED 以精简照明设计流程(11-26)

- 基于改进的遗传算法软硬件划分方法研究(07-20)

- 锂电池均衡处理技术解决SOC和C/E失配问题(06-28)

- PSoC3应用于多通讯接口时的DMA设计 (03-05)