一种低功耗64倍降采样多级数字抽取滤波器设计

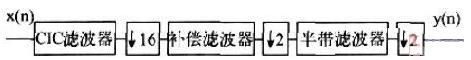

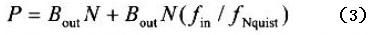

通带纹波仍满足指标要求,补偿滤波器同时还具备降采样抽取功率,可选择4 倍抽取,也可先进行2 倍抽取,然后用一级半带滤波器再完成2 倍抽龋基于多级抽取有利于降低硬件资源与功耗的原则,64倍降采样数字抽取滤波器可采用如图1 所示的三级结构。

图1 系统结构框图

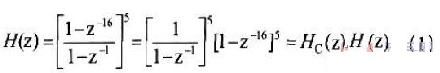

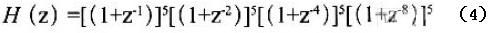

CIC 降采样滤波器对系统性能的影响至关重要,其级联级数D与S-Δ调制器的阶数L之间存在D=L+1的关联,对于4 阶∑-△调制器,D=5,在16 倍降采样率下,CIC 滤波器的系统函数为:

采用Hogenauer 经典结构实现以上系统传输特性时,可将级联梳状滤波器分解为积分器HC(z)与梳状微分器HI(z)两部分,然后采用层叠结构实现。

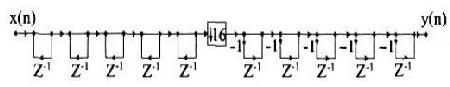

由于HI(z)中的延迟因子需要16 个寄存器,采用置换原则,完成16 倍抽取后再进行微分部分的计算,这样就只需要一个延迟因子,由此得到如图2 所示的经典CIC 电路结构框图。

图2 经典CIC滤波器电路结构

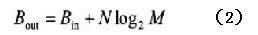

CIC 中由于没有乘法运算,同时置换原则的应用大大减少了寄存器的数量,面积和功耗得到有效控制。但是,经典CIC 结构的很大缺陷在于其中的积分器HC(s)为IIR 滤波器,即存在的输出到输入反馈使系统稳定性无法保证,并导致数据溢出。设CIC 滤波器的级联级数为N,抽取倍数为M,输入与输出位数分别为Bin 和Bout,则两者间必须满足以下关系:

根据设计指标要求,Bin=1bit、M=24、N=5 时,Bout=21bit,即整个电路中所有寄存器和加法器位数为21 位时,系统才不会产生溢出,而输出位数的大小决定了寄存器的位数以及涉及的计算量,并由此影响功耗与面积。

最终决定数字滤波器面积的是寄存器单元数量,通过估算其中1 位寄存器的数量可比较芯片面积的相对大小;由于没有乘法器,则加法运算决定了CIC 滤波器中的功耗,以1 个1 位加法器在一个输出周期内完成的加法次数作为估算功耗的基本单位。

图2 中,一共有10 个延迟因子,若每个字长均取21 位,一共需要210 个1 位寄存器。总共有10 个21 位加法器,5 个工作在输入频率,5 个工作在输出频率,等效功率因子为:

计算得到等效功率相对因子为6 825,较大的功耗表明针对功耗面积优化的CIC 尚有继续改进的空间。

3.CIC 滤波器的改进设计

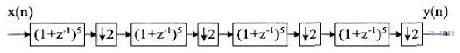

经典CIC中IIR传递函数的递归结构严重制约了CIC 滤波器的性能,消除IIR 成为改进CIC 设计的基本出发点。将H(z)中的分子多项式因式分解并通过约分得到:

上式中没有IIR 结构,从而消除了输出到输入的递归运算,确保系统稳定,结合置换原则,由此得到改进的CIC 电路结构如图3 所示。

图3 非递归结构CIC滤波器的实现框图

这种非递归结构所需要的1 位寄存器总数为R=1+2+3+?+20=210,而等效功耗因子P=(2+3+4+5+6)×16+(7+8+9+10+11)×8+(12+13+14+15+16)×4+(17+18+19+20+21)×2=1 130。与经典结构相比,寄存器总数相等,但功耗减小到原来的1/ 6,采用这种非递归结构不但改善了系统稳定性,还大大提高了系统性能。由于电路实现时需采用层叠结构,5级结构即需5 级层叠,如果其中有一级为4 或者更小,那就可以减小层叠数,从而进一步减小硬件和功耗。

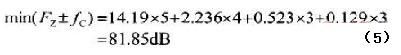

阻带衰减为衡量CIC 滤波器性能的一个重要指标。通过牺牲部分阻带衰减性能可减小层叠数。对于4 级结构,应分别考虑各级在需要的衰减频段处能达到的衰减值。在Matlab下分别仿真(1+z-8)、(1+z-4)、(1+z-2)、(1+z1)的幅频特性,并依次设为第一级到第四级。设CIC 滤波器的零点为FZ,根据设计指标,中心频率fC=22kHz,只要在所有FZ ± fC频率范围内阻带衰减值能达到80dB,CIC滤波器即可满足设计指标要求。由于最小衰减值出现在FZ-fC 与FZ+fC 关键频率点处,在Matlab 下仅测试单级时关键频率点处的阻带衰减。

通过计算,当第一级到第四级的级联级数分别减小为最低的5、4、3、3 时,则最小阻带衰减量计算为:

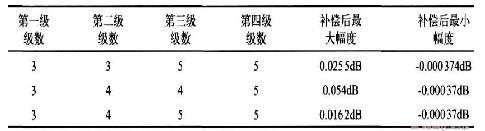

虽然以上降低层叠数的改进结构其最小阻带衰减满足设计要求,但后级补偿滤波器无法使纹波达到设计要求,应加大其中一级或两级的级联级数来降低补偿后的通带纹波,将级数增大后纹波的变化如表2 所示。

表1 级数增大后补偿结果的变化

只有当级联级数为3、4 、5 、5 时补偿后的结果接近设计指标要求。将补偿后的整体幅频特性沿着Y 轴方向向下移动约0.008dB 左右,这样最大纹波为0.016 2-0.008=0.008 2dB,最小纹波为-0.000 37-0.008=-0.008 37dB,这样纹波就在指标范围内,所以采用

- RS-485网络设计降低功耗问题(01-26)

- 低功耗CMOS电压基准源的设计(08-27)

- 一种新型低功耗两级运算放大器的实现(01-20)

- 创建理想的低功耗设计(01-14)

- 新一代电池供电装置的超低功耗设计(07-18)

- 基于绝热逻辑的低功耗乘法器电路设计(07-23)