ADC中的集成式容性PGA:重新定义性能

ADI专利的容性可编程增益放大器(PGA)相比传统的阻性PGA具有更佳的性能,包括针对模拟输入信号的更高共模电压抑制能力。

本文描述了斩波容性放大器的工作原理,强调了需要放大传感器小信号至接近供电轨--比如温度测量(RTD或热电偶)和惠斯登电桥--时,此架构的优势。

Σ-Δ型模数转换器(ADC)广泛用于传感器具有较小输出电压范围和带宽的应用中(比如应变计或热敏电阻),因为这种架构提供高动态范围。具有高动态范围是因为,相比其它ADC架构,它具有低噪声性能。

Σ-Δ型转换器基于两条原理工作:过采样和噪声整形。当ADC对输入信号进行采样时,独立于采样频率的量化噪声会在直到采样频率一半的整个频谱内扩散。因此,如果输入信号以比奈奎斯特理论所推导出的最小值高很多的频率采样,则目标频段内的量化噪声下降。

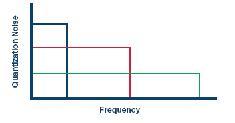

图1显示了不同采样频率下的量化噪声密度示例。

图1.不同采样频率下,频率范围内的量化噪声密度。

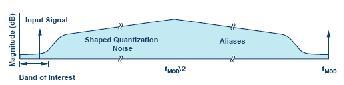

一般而言,对于特定的目标频段,每2个过采样系数就会使动态范围改善3 dB(假定为白噪声频谱)。Σ-Δ型转换器的第二个优势是噪声传递函数。它将噪声整形至更高频率(如图2所示),进一步降低了目标频段内的量化噪声。

图2.Σ-Δ噪声整形。

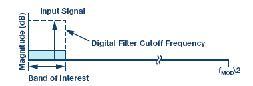

此外,Σ-Δ架构可能集成数字滤波器,用来移除目标频段外的量化噪声,实现出色的动态范围性能,如图3所示。

图3.LPF之后的量化噪声。

输入缓冲器

过采样架构的缺点之一是,相比其它采样频率较低的架构,驱动Σ-Δ型调制器的输入缓冲器要求可能会更严格。采集时间变得更短,因此缓冲器需要更高带宽。现代Σ-Δ型转换器片上集成输入缓冲器,最大程度简化使用。

此外,在检测系统中,为检测元件提供具有高精度的极高输入阻抗对于测量精度而言极为关键。这使得输入缓冲器的要求更为严格了。

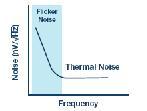

集成输入缓冲器还有其它挑战。Σ-Δ型调制器可在低频率时提供极低噪声,但所有其它元件(比如输入缓冲器)都会使热噪声增加,而更严重的则是低频闪烁噪声,如图4所示。

图4.闪烁噪声。

此外,缓冲器失调也可能增加总系统误差。通过系统校准可以补偿失调,但如果失调漂移相对较高,那么这种方式就无法实现,因为每次工作温度发生改变都会要求系统重新校准,以补偿缓冲器失调。

例如,当失调漂移为500 nV/°C时,10°C温度递增将等于5 µV失调范围,在±2.5 VREF 24位ADC中这相当于16.8 LSB,即约为4位。

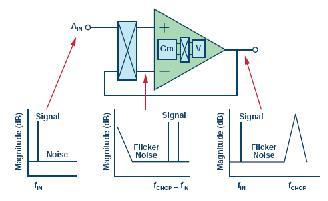

解决这两个问题的典型途径是对缓冲器的输入和输出进行斩波,如图5所示。

图5.斩波放大器。

对输入进行斩波之后,输入频率便调制到较高频率。缓冲器失调和闪烁噪声依然保持其最初的低频率,因为它们不受输入斩波的影响。

输出去斩波机制将输入频率解调回基带,同时向上调制缓冲器产生的失调和闪烁噪声至较高频率,随后由ADC低通滤波器加以消除。

某些情况下,输入缓冲器可以采用基于电阻的仪表放大器(阻性PGA)来代替,以使小传感器信号满足全调制器输入范围,最大程度提升动态范围。需注意,基于电阻的仪表放大器相比差分阻性放大器是更好的选择,因为分立式传感器需要更高的输入阻抗。阻性PGA可实现类似的斩波方案,如图6所示。

图6.阻性PGA。

阻性PGA可能需要级联第二组缓冲器,因为放大器可能无法提供直接驱动调制器所需要的足够带宽。同时,必须保持低功耗,这就确定了

电阻值,进而确定了放大器带宽。

使用这种放大器拓扑的主要问题是,它限制了共模电压--尤其是在增益大于1的时候,因为阻性PGA具有取决于输入信号的浮动共模值,如图6所示。

此外,阻性网络失配及其漂移也是影响总误差预算的因素之一,因为它可能会影响大多数的精度规格。

为避免这些限制,最新的Σ-Δ型转换器采用了容性PGA。

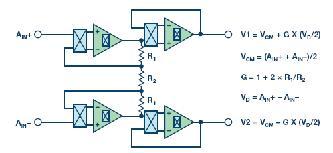

容性PGA放大原理与阻性PGA相似:增益取决于电容比,如图7所示。

为了放大直流信号,容性PGA在PGA输入端引入了斩波机制直流输入信号调制到斩波频率,然后由容性放大器进行放大。最后,信号通过输出去斩波解调回直流。此外,放大器失调和闪烁噪声调制到斩波频率,并在之后的级中进行低通滤波。

图7.容性PGA(为简便起见,移除了部分模块)。

相比阻性架构,这种容性架构有一些优势:

它能更好地权衡噪声与功率,因为噪声源较少。需要较少的放大器,而且相比电阻,电容不会产生噪声。

电容比电阻有非常多的优势。除了无噪声外,电容不会受到自发热影响,且通常具有更好的匹配和温度漂移

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 12位串行A/D转换器的原理及应用开发(10-09)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 深入解析:模拟前端模/数转换器的三种类型 (11-26)