详解TPS5432x/62x, TPS54x18/x19低电压输入下电二次启动问题

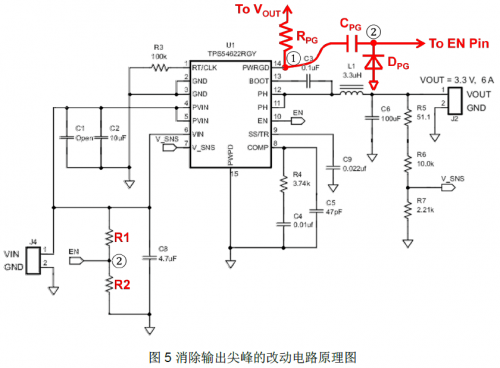

本变通解决方案在原有EVM板电路基础上增加了RPG、CPG 和DPG 三个元件,由于TPS54622 具有电源正常(Power Good, PG)输出指示功能,且当输出电压低于稳压输出的92%或高于稳压输出的106%时,就会驱动PG 引脚使其拉低。本方案的思路是利用电容两端电压不能突变的原理,在PG 引脚和使能EN 引脚之间跨接一无极性电容器,当输出电压跌落低于稳压值的92%时,PG 引脚变低,同时将使能EN 引脚拉低,从而在输入电压反弹的时间段内能够保证使能EN 引脚电压低于开启电压,彻底关闭芯片输出。由于PG 引脚为漏极开路结构,电阻RPG 用于上拉PG 引脚,取值为10kΩ~100kΩ 之间,电容CPG 取值为1uF 即可,取值过大需要较长放电时间,过小无法将使能EN 引脚彻底关闭。

因此,节点②处的电压理论上瞬间将会跳变为-1.436V,实际测试该节点电压约为-0.9V(如图6所示)。该负电压超出了器件手册规定的最大极限值-0.3V 的范围,会造成芯片损坏。为了避免该情况的发生,节点②处的EN 使能引脚需要对地增加一反向肖特基二极管DPG 进行电压钳位保护。

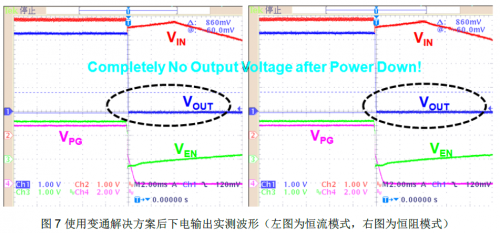

最终本电路在相同测试条件下测试波形如图7 所示。从图7 中可以看出VOUT 在下电之后由于EN引脚被彻底拉低使得芯片完全关闭输出,从而彻底消除了输出尖峰问题。

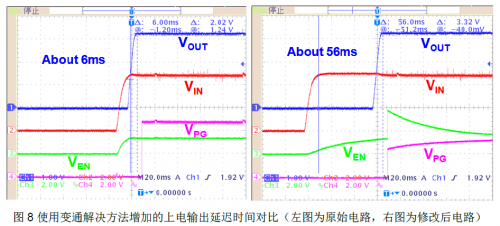

值得注意的是,由于增加一个电容连接在EN 引脚,上电时有一定的电容充电时间,从而会引起输出电压的延迟,实际测试的延迟时间对比图如图8 所示,从图中可以看出,采用本解决方法后会增加约50ms 的输出延迟时间。

4 结论及总结

本文研究了TPS54622 在低电压输入情况下输入电源下电后输出电压出现二次启动并产生较大尖峰问题,并且该问题实测发现同样存在于TPS5432x/62x 系列和TPS54x18/x19 系列器件中。本文对该问题产生的根源进行了分析并给出了一种消除该尖峰的简便易行解决方法,实际测试该方法彻底消除了下电后输出电压的二次启动过冲尖峰现象。

TPS54622 SWIFT 德州仪器 二次启动 相关文章:

- 8位高速A/D转换器TLC5510的应用(02-16)

- 改善平板显示器的音频性能(02-13)

- 运算放大器的选择(03-18)

- 单端数字音频放大器设计和应用考虑的要素(05-19)

- 为网络监控摄像机设计合适的电源(05-20)

- 改善可编程增益放大器性能的一个技巧(05-21)