SoC电源管理中调节器面临的命运

越来越复杂的SoC在一个管芯中集成很多系统组件 ,这在总体上简化了系统设计人员的工作。但是这些芯片也导致电源供电子系统越来越复杂。以前从供电连接器到IC连接Vcc的布线是非常简单的任务,而现在却成为与系统中其他部分一样复杂的有源网络设计。

SoC的供电要求越来越高,使得这种设计也越来越复杂。好在设计人员可以选择在电路板级来处理这些任务,SoC开发人员希望将电源网络组件置入到芯片中以期有所帮助。但是最终,电源设计人员仍然要做出一些很难的决定。在决定之前,他们要进行一些模拟电路仿真工作。

不断增长的需求

集成是有成本的。 SoC设计人员在其图纸上画出各种电路,这类电路都有自己的电压、噪声、排序和瞬变响应要求。移植到尺寸更小的电路上不但能够实现集成,而且还降低了供电电压。这一发展趋势也同时增大了峰值工作电流、缩小了噪声余量,使得动态电源管理越来越复杂。

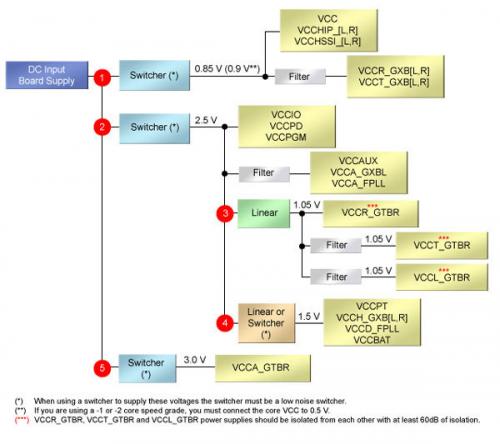

复杂度的提高最明显的结果就是SoC使用的外部电源数量迅速增加 ( 图1 ) 。例如,一片高端FPGA会有15条外部驱动的电源轨。它们都连到哪里?

图1. 一片现代SoC需要很多不同的供电线路,每条线路都有自己的稳压和调理要求。

答案之一是不同的电压需求。在FinFET工艺出现之前 , 内核逻辑供电电压一直在大幅度降低 , 但在1V附近却停滞不前。而其他类电路在这方面远远落在了后面。按照工业标准, I/O单元只能使用特定的供电电压。SRAM单元需要的电压要比逻辑级稍高一些,以保证可靠的全速工作,待机时的电压要低很多。高精度模拟电路希望有较高的电压以降低抖动,提高噪声余量。这些各种各样的需求导致供电线路数量的急剧增长。

但是 , 电压数量还不是唯一的问题。某些SoC电路--特别是低噪声放大器、锁相环(PLL) ,以及物理接口等都有非常严格的供电噪声限值。即使电压相同,这些需求也导致电路无法共享同一条噪声源供电线路,例如,数字逻辑或者大电流I/O单元等。因此,需要增加低噪声电源。

非常有意思的是,增加供电线路的另一需求是来自电源管理。数字设计人员越来越多的采用了动态低功耗技术--例如,精细粒度时钟选通、随时供电选通和电压调整等,使用这类技术的电路对其供电线路瞬变响应的要求特别高。负载在微秒甚至更小的量级上变化。为能够响应来自SoC的命令,电压应不断变化。这些负载实际上可以采用不同的恒定电压源或者噪声敏感电压源。

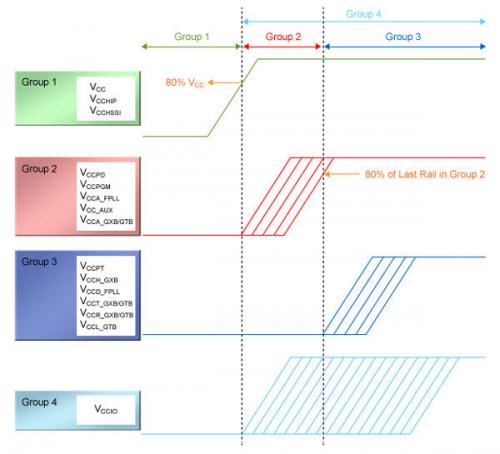

排序也需要单独的供电线路(图2) 。在很多SoC中,对上电顺序有要求--在某些情况下,对关电顺序也有要求。这种时序要求使得电路提供不同的供电线路,不然可以共享一个电源。

图2. 正如这一FPGA所示,复杂的SoC上众多的电源线,通常都有严格的上电排序要求。

找到策略

系统设计人员会面对SoC上大量不同的电源线 , 遇到棘手的问题。据Altera公司电源业务部研究员兼首席技术官Ashraf Lotfi,解决方法一般是采用某种分布式电源网络。

"一般而言,您会看到在电路板上有体积较大的调节器,对系统的12 V或者24 V进行降压,将其分配给每一个负载点调节器。为满足各种需求,您通常都会针对每一电源线提供负载点供电。 "

由于电源线数量的快速增长,每一新设计都要求进行分析, 以减少调节器的数量。一块电路板上15条电源线还不够理想。因此,设计人员需要解决一些关键问题。在这种特殊的实现中,这些电源线的电压、噪声和排序要求能够支持它们共享一个调节器吗? 如果不能,是否可以采用一条电源线,以稍微不同的电压运行,从而共享调节器--即使是以稍高的功率代价或者稍微降低一些性能?外部排序转换器能有所帮助吗?

Lotfi说 , 减少了调节器数量后 , 设计人员可以把注意力转向优化调节器效率和布局。只要噪声和瞬变响应要求允许,那么,最好的起点是使用高效开关调节器,而不是线性调节器。Lotfi认为,最近的高频开关模块极大的扩展了范围,使得这类替换成为可能。

设计人员还可以针对每一调节器的要求尽量减小电路板面积。模块化结构可以在一个混合封装中实现控制器、电压参考、驱动、电源FET ,以及电感。在某些设计中,反馈补偿也含在封装中。原理上,这种集成使得设计人员不能自由的优化调节器的传送功能,以满足某种电源的特殊需求。而在实际中, Lotfi主张,需要电源设计人员提供反馈无源功能,占用较多的设计时间,增加电路板面积,从而提高灵活性,这样做是值得的。供应商可以为调节器内部组件预设最优传送函数,满足一般要求。Lotfi宣称,而且,把关键组件放到模块中,调节器供应商可以提高开关频率,提高总效率,有效的

- 350-W、双相交错式预调节器设计评价(08-01)

- 驱动中型LED背光系统的集成方案(10-03)

- 提高电源转换效率的交错式PFC控制技术及应用(04-06)

- MAX8686电流模式同步整流PWM降压调节器 (09-25)

- 电池供电系统中DC-DC升压调节器的应用(10-01)

- 为MCU风扇调速器供电的交流线路(06-04)