AMC1204的应用指南

器实现比较简单,不需要单独增加DSP 或FPGA 即可实现。但是,移动平均滤波器的频域效果较差,滚降较慢,因此,在检测低频信号及对精度要求不高的应用中,可以考虑使用这种方法。但是,对于精度要求比较高的应用中,需要考虑使用性能更好的滤波器,如Sinc 滤波器。

3.2、Sinc 滤波器

Sinc滤波器具有良好的频域特性,较低的成本和功耗,延时较低,因此,广泛用作Delta-Sigma DAC 的滤波器。Sinc 滤波器可通过专门的滤波器芯片或者通过FPGA 或DSP 算法来实现。

AMC1210 是一个4 通道的数字滤波器,芯片输出接口可设置为SPI 接口或者并行接口方式,方便与CPU 进行数据通信。数字滤波器可设置为Sincfast, ,

, 或者

或者 方式。实际应用时,由于

方式。实际应用时,由于 滤波器具有更好的低通特性,建议将AMC1210 配置为

滤波器具有更好的低通特性,建议将AMC1210 配置为 滤波器,过采样率(OSR)设为256以获得最优的转换结果。

滤波器,过采样率(OSR)设为256以获得最优的转换结果。

图6 AMC1204 与AMC1210 的连接

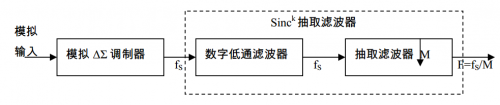

此外,也可以通过FPGA 或DSP 来实现Sinc 滤波器算法。滤波器的基本架构如图7 所示。

图7 调制器与抽取滤波器的基本架构

以下是用VHDL 语言实现SINC3 滤波器的一段示例程序。其中,CNR=MCLK/M,M 为抽取率(即过采样率OSR)。

图8  数字滤波器架构

数字滤波器架构

图8 的示例代码:

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity FLT is

port(RESN, MOUT, MCLK, CNR : in std_logic;

CN5 : out std_logic_vector(23 downto 0));

end FLT;

architecture RTL of FLT is

signal Z1 : std_logic_vector(23 downto 0);

signal Z2 : std_logic_vector(23 downto 0);

signal Z3 : std_logic_vector(23 downto 0);

signal Z4 : std_logic_vector(23 downto 0);

signal Z5 : std_logic_vector(23 downto 0);

signal Z6 : std_logic_vector(23 downto 0);

signal Z7 : std_logic_vector(23 downto 0);

begin

process(MCLK, RESN)

begin

if RESN = '0' then

Z1 <= (others => '0');

Z2 <= (others => '0');

Z3 <= (others => '0');

elsif MCLK'event and MCLK = '1' then

Z1 <= Z1 + MOUT;

Z2 <= Z2 + Z1;

Z3 <= Z3 + Z2;

end if;

end process;

process(CNR, RESN)

begin

if RESN = '0' then

Z4 <= (others => '0');

Z5 <= (others => '0');

Z6 <= (others => '0');

Z7 <= (others => '0');

elsif CNR'event and CNR = '1' then

Z4 <= Z3;

Z5 <= Z3 - Z4;

Z6 <= Z3 - Z4 - Z5;

Z7 <= Z3 - Z4 - Z5 - Z6;

end if;

end process;

CN5 <= Z7;

end RTL;

4、结论

应用高性能隔离Delta-Sigma调制器AMC1204时,为了确保转换精度,需要注意外围输入电路的设计,选择合适的输入采样电阻以及时钟频率,使得输入采样电阻阻值相对于输入等效阻抗尽量小,以此降低输入电阻引起的转换误差;同时选择合适的输出滤波器,以满足整个系统对测量精度的要求。

5、Reference

[1] AMC1204 datasheet

[2] AMC1210 datasheet

AMC1204 隔离Delta-Sigma调制器 德州仪器 相关文章:

- 8位高速A/D转换器TLC5510的应用(02-16)

- 改善平板显示器的音频性能(02-13)

- 运算放大器的选择(03-18)

- 单端数字音频放大器设计和应用考虑的要素(05-19)

- 为网络监控摄像机设计合适的电源(05-20)

- 改善可编程增益放大器性能的一个技巧(05-21)