一种新型数字SPWM信号的设计与实现

,反之则需要较长的死区时间才能保证功放管的安全工作。本设计采用的死区控制策略是:"提前关断、延迟导通",如图3所示,在单相两路的系统中,对于第一路是将原始脉冲的上升沿的时间推迟一段时间(死区时间),下降沿不变,而第二通道是把原始脉冲先反相,反相后的脉冲下降沿不变,而上升沿推迟一段时间(死区时间)。

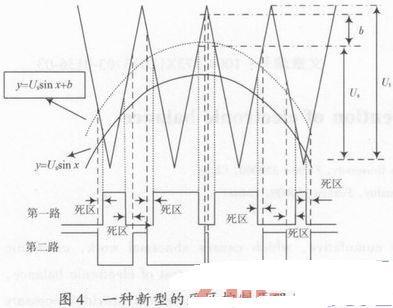

软件实现方法与脉冲消去方法大致相同,一般都是设计一个加减计数器,根据死区时间来确定加减计数器的最大值d,由计数器的最大值d来确定死区时间。这种实现方法是一般的实现方法,本设计提出了一种新型的死区产生方法,如图4所示,实线表示正常采用自然采样法的正弦波形和三角波形,正弦波y=Ussin x的半波的幅度为Us,三角波的幅度为Ut,根据自然采样法的原理,这里假定正弦波大于三角波时输出为高电平,小于时输出为低电平,根据正弦波和三角波的交点及电平输出的判断规则可以得到SPWM脉冲的第一路波形,这时把正弦波向上平移b个单位,如图4中的虚线,正弦波形y=Ussin x变为y=Ussinx+6,再根据自然采样法的原理用平移后的正弦波和三角波相交,根据交点判断输出高低电平,这样判断输出的电平高低就可以得到第二路的SPWM波形,生成了SPWM波形的死区,在本设计中采用的是数字方法产生SPWM,根据图4,可以在程序中按原来的方法产生第一路信号,把从ROM中取出的正弦信号加上b,再和原来的方波信号进行比较,这样就可以得到第二路SPWM信号,同样道理,也可以把三角波向上平移b个单位来产生第二路SPWM信号,但不管平移正弦波或三角波,都要保证平移后的正弦波的波形幅度要小于三角波的波形幅度。也可以设计第三个ROM,在程序外把经过向上平移后的正弦波形进行量化,存入ROM表中,在程序中用这个表和三角波的离散值进行比较,只是这样设计会增加FPGA硬件资源的消耗和增大存储器的存储空间。

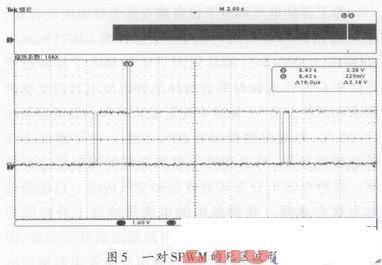

正弦信号往上偏移值b的确定是根据死区时间的值来确定的,这个值越大,则死区时间也越长,所以,可以调节b的值来增大或减小死区时间。一对经过死区处理后的SPWM波形如图5所示,从图5中可以看出,死区时间为16μs.

1.3脉冲消去模块

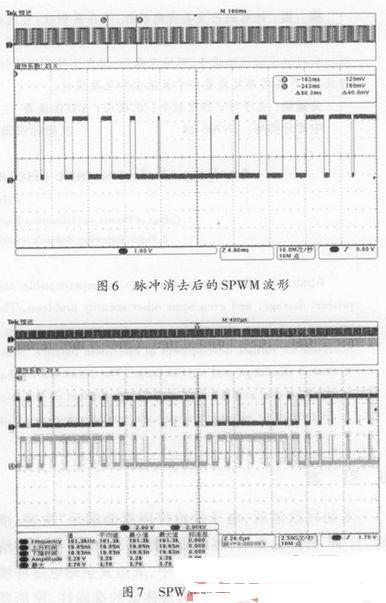

在产生的SPWM脉冲中,完整的SPWM脉冲序列包含了占空为从0~100%的脉冲,因此有些脉冲的宽度可以达到非常小,而实际上,过窄的脉冲是无用的,因为在这样短的脉冲持续时间内,后级的功率放大管是不能完全导通或关断,只会增加功率器件的损耗,所以必须删除这些不良窄波;如图4所示,第二路的SPWM波形会出现比第一路SPWM波形小两倍死区时间的脉冲,如果某个脉冲已经在临界的宽度了,经过死区产生模块就会变成一个对后级的功率管来说过窄的脉冲,这也就是脉冲消去模块在死区模块后级的原因,它的作用是消去一些本来就有的和经过死区处理后的毛刺。处理后的波形如图6所示,图7为处理后的一对带死区的SPWM波形。

不论采用这种方法产生的SPWM波形,还是利用加减计数器的方法来产生SPWM波形,经过脉冲消去模块,都会存在输出的两路SPWM脉冲不对称性问题,如图7所示,就是有可能其中一路的波形缺失或所对应的另一路波形出现缺失,但这个问题可以在脉冲消去后再加一个模块进行处理而避免;对于载波频率变小时负载谐波变大的问题可以参考器件参数采用一定频率范围内的动态载波比和动态死区时间来解决。

2 结语

本文设计了一种基于FPGA的带死区的SPWM波形产生技术,对于SPWM的死区产生,一般都是应用加减计数器来实现,本文提出了一个新的选择,把死区产生模块融合到了比较模块中,利用波形平移技术,巧妙的产生了所要求死区时间的SPWM波形。生成的SPWM波形输出给后级的功率放大电路,检测系统负载上的电压和电流波形为较好的正弦波形,很好地满足了设计的要求。

- 电源管理总线的结构与优势(11-19)

- 新型灌封式6A至12A DC-DC μModule稳压器系列(11-19)

- 低电压PLD/FPGA的供电设计(01-24)

- 基于FPGA的高精度数字电源(02-12)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)