讨论在PFC中应用的新型超级结MOSFET器件的特点

超级结(Super-Junction)MOSFET器件基于电荷平衡技术,在减少导通电阻和寄生电容两方面提供了出色的性能,这通常需要折中权衡。有了较小的寄生电容,超级结MOSFET具有极快的开关特性并因此减少了开关损耗。自然地,这种快速开关特性伴有极高的dv/dt和di/dt,会通过器件和印刷电路板中的寄生元件而影响开关性能。特别地,对于在现代高频SMPS中使用的超级结MOSFET,很难抑制频率噪声和EMI辐射,同时实现高开关效率和低开关噪声。此外,开关噪声会导致某些意外的系统或器件失效,它们与栅氧化层击穿、dv/dt衰减和控制信号中的闩锁效应问题相关,因为在各种异常状况中,例如启动状态、过载状况和并联工作,会发生严重的栅极振荡和高开关dv/dt.为实现低开关噪声,需要使用高值寄生电容或栅电阻。根据最近的系统发展趋势,改进效率是一个关键目标;然而,只为降低开关噪声而使用慢速开关器件不是最佳解决方案。凭借SuperFET II MOSFET的优化设计,新一代超级结MOSFET SuperFET II器件实现了快速开关和低开关噪声,在应用中达到了高效率和低EMI.

SuperFET II MOSFET技术

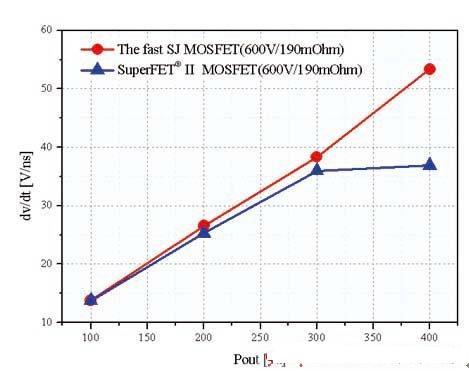

众所周知,超级结MOSFET的高开关速度自然有利于减少开关损耗,但它也带来了负面影响,例如增加了EMI、栅极振荡、高峰值漏源电压。在栅极驱动设计中,一个关键的控制参数就是外部串联栅电阻(Rg)。这会抑制峰值漏-源电压,并防止由功率MOSFET的引线电感和寄生电容引起的栅极振铃。该器件还在导通和关闭过程期间降低电压上升速率(dv/dt)和电流上升速率(di/dt)。但Rg也会影响MOSFET的开关损耗。因为器件必须在目标应用上达到最高效率,控制这些损耗是重要的。因此从应用的观点出发,选择正确的Rg值是非常重要的。SuperFET II MOSFET使用了集成栅电阻,它不是等效串联电阻(equivalent series resistor,ESR),只是栅电阻,置于栅极焊盘中,以便减少栅极振荡和控制大电流条件下的开关dv/dt与di/dt.集成栅电阻数值采用栅电荷来优化。器件的真实栅极中,VGS的栅极振荡(Vb)显著减少了,因为栅-源端的电压降由内部Rg和外部Rg来分担。反向传输电容Cgd是影响开关期间的电压上升和下降时间的主要的参数之一。Cgd提供了来自漏电压的负反馈作用,它必须由通过Rg的栅极驱动电流来放电。振荡与几个原因有关,例如高的开关dv/dt和di/dt、寄生Cgd和漏极电流值。SuperFET II MOSFET的栅极电荷已优化,用于改进开关效率和开关噪声之间的折中权衡。图1显示了在关断瞬态期间,在相同驱动条件下,从100W至400W的PFC电路中,比较快速SJ MOSFET和SuperFET II MOSFET之后,实际MOSFET的dv/dt.关断dv/dt呈线性上升,对于小的栅电阻(3.3Ω),快速超级结MOSFET显示了在PFC电路中dv/dt不受控制。相比快速超级结MOSFET,SuperFET II MOSFET减少了关断dv/dt的增加,但在300W负载条件下仍然呈线性增加。在满负载条件下,dv/dt可控制在36V/ns,相比快速超级结MOSFET,dv/dt减少了约30.8%.

图1在关断瞬态期间,PFC电路中快速SJ MOSFET和SuperFET II MOSFET的dv/dt测量比较(VIN=100Vac,PO=400W,Rg=3.3Ω)

超级结MOSFET的寄生振荡机制

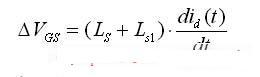

超级结MOSFET的Coss曲线是高度非线性的。当超级结MOSFET作为开关器件用于PFC或DC/DC转换器时,这些影响将会产生极快的dv/dt和di/dt以及电压和电流振荡。图2显示了观察到的PFC电路中的振荡波形,它们出现在超级结MOSFET关断瞬态期间。从一般的观点来看,有几种振荡电路会影响MOSFET的开关性能,包括内部和外部振荡电路。图3显示了简化的PFC电路原理图,包括内部寄生参数,这是由功率MOSFET本身的寄生电容Cgs、Cgd_int.和Cds与寄生电感Lg1、Ld1和Ls1,以及外部振荡电路,由外部耦合电容Cgd_ext.和线路板布局的寄生电感LG、LD和LS带来。寄生元件更多地涉及到开关特性,因为开关速度变得更快。当MOSFET导通和关断时,会在谐振电路中产生栅极寄生振荡,该谐振电路由内部和外部栅-漏电容Cgd_int.和Cgd_ext.以及栅电感Lg1和LG组成。当MOSFET开关速度变快时,尤其在它关断时,由于寄生电感LD,MOSFET漏-源中的振荡电压会经过栅-漏电容Cgd,并形成了包含栅电感Lg1和LG的谐振电路。由于栅电阻极小,振荡电路Q()变大,当谐振条件出现时,在那个地方和Cgd或LG、Lg1之间产生了大振荡电压,并引起了寄生振荡。此外,LS和Ls1两端的电压降可由公式(1)表示,它由关断瞬态期间的负漏极电流引起。杂散源极电感LS和Ls1两端的电压降在栅-源电压上产生了振荡。寄生振荡会引起严重的EMI问题、大的开关损耗、栅-源击穿、栅极失控,甚至导致MOSFET失效。

(1)

(1)

PFC 超级结MOSFET SuperFET II MOSFET 相关文章:

- 高效率PFC电路二极管选择方案(01-24)

- 什么是PFC电路?(11-03)

- 采用开关器件提高PFC效率(06-23)

- 飞兆半导体交错式临界导通PFC控制器为绿色电源提供超过96%的效率(01-20)

- 如何实现高功率密度的工业电源(05-10)

- 无源无损软开关功率因数校正电路的研制(07-03)