直接数字频率合成器DDS的优化设计

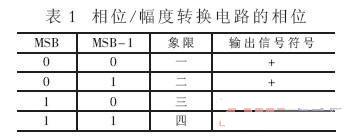

相位/幅度转换电路是DDS电路中的另一个关键部分,设计中面临的主要问题就是资源的开销。该电路通常采用ROM结构,相位累加器的输出是一种数字式锯齿波,通过取它的若干位作为ROM的地址输入,而后通过查表和运算,ROM就能输出所需波形的量化数据。考虑到正弦函数的对称性:在[0,2π]内,正弦函数关于x=π成奇对称,在[0,π]内,关于x=π/2成轴对称。因此,在正弦查找表中只须存储相位在[0,π/2]的函数值。这样,通过一个正弦码表的前1/4周期就可以变换得到整个周期码表,节省了近3/4的资源,非常可观。具体实现如表1所示,为节省ROM资源,取相位累加器输出的高8位做为ROM的输入地址,其中最高位(MSB)控制对输出信号符号的处理,次高位(MSB-1)控制对输入地址的处理。

当MSB-1为‘0’(一,三象限)时,对查找地址phase(5……0)不做任何处理;当其为‘1’(二,四象限)时,对phase(5……0)取反。ROM的输出为10位数据,其中最高位为符号位。当MSB为‘0’(一,二象限)时,输出信号符号位为‘0’,低9为ROM中的幅度数据;当其为‘1’(三,四象限)时,输出信号符号位为‘1’,低9位为ROM中的幅度数据的相反数的补码。ROM的VHDL实现的主要部分如下:

architecture Behavioral of rom is

signal sin:STD_LOGIC_VECTOR(8 downto 0);

signal temp:STD_LOGIC_VECTOR(5 downto 0);

begin

temp<=phase when MSB-1=′0′ else

not phase;

process(temp)

begin

case temp is

when ″000000″=>

sin<=″000000000″;

…… --正弦查找表由MATLAB生成

end case;

end process;

data_out<=″0″ & sin when MSB=′0′ else

″1″ & not sin+″000000001″;

end Behavioral;

2.3 同步接口电路设计

在使用DDS时,需要为其提供频率控制字K的值,一般通过中央控制单元MCU来完成,其以数据总线及写时钟信号的方式与FPGA内的DDS实体进行通讯,同时DDS在FPGA内部又是在本地时钟fc驱动下运行。由于MCU的写时钟和FPGA内的本地时钟异步,两者之间进行通讯难免存在数据不稳等问题,特别是在通讯速度较高时,这一异步接口问题会更加突出。为了实现异步接口的同步化,本文提出了如图3所示的接口同步电路。

3 硬件实现及仿真结果

本文使用VHDL 语言对各个模块及DDS系统进行描述。顶层文件如下所示:

Entity dds is

Port(reset:in std_logic;--全局复位信号

fre:in std_logic_vector(7 downto 0);

--频率控制字输入

clk:in std_logic;

--系统时钟

fwwrn:in std_logic; --频率控制字写信号

gen:in std_logic_vector(0 downto 0);--波形控制字

amp_out:out std_logic_vector(9 downto 0));

--正弦波幅度输出

end dds;

architecture Behavioral of dds is

component fcwld--接口同步模块

Port(reset:in std_logic;

clk:in std_logic;

fre:in std_logic_vector(7 downto 0);

fwwrn:in std_logic;

syncfreq:out std_logic_vector(31 downto 0));

--合成频率控制字

end component;

component accumulator --流水线累加器块

Port(reset:in STD_LOGIC;

clk:in STD_LOGIC;

syncfreq:in STD_LOGIC_VECTOR(31 downto 0);

phase:out STD_LOGIC_VECTOR(7 downto 0));

--相位高八位输出

end component;

component rom--波形存储器模块

Port(phase:in STD_LOGIC_VECTOR(7 downto 0);

gen:in STD_LOGIC_VECTOR(0 downto 0);

amp_out:out STD_LOGIC_VECTOR(9 downto 0));

end component;

为了对DDS进行*估,将以上设计在Xilinx公司的开发软件中进行了设计及优化,目标器件为其最新的90nm工艺器件Spartan3E中最小器件XC3S100E-4VQ100C,该设计所占用的FPGA资源如表2所示。

由表2可以看出,本文给出的DDS设计占用资源很少,由于XC3S100E的市场价格在2美金左右,故本设计所占的硬件成本可以缩减到0.2美金左右。同时在ISE8.2中该设计的系统时钟最大达到159.6MHz。以上的设计性能几乎和现有的专用芯片相当,但成本下降很多。

为了进一步验证本文给出的DDS设计系统在功能和时序上的正确性,对其进行了时序仿真,使用的仿真软件为Modelsim6.1。仿真结果表明,该DDS系统可以运行在较高的工作频率下。

本文在对DDS的基本原理进行深入理解的基础上,通

数字频率合成器 DDS FPGA 相位 幅度转换 相关文章:

- 如何预测直接数字频率合成器(DDS)输出频谱中主相位截断杂散的频率和幅度(06-18)

- 一种基于AD9857的信号发生器的设计(09-07)

- 基于FPGA及DDS技术的USM测试电源的设计 (09-08)

- 高性能双通道DDS芯片AD9958及其应用(02-04)

- 基于DDS的调频信号发生器的设计与仿真(04-12)