LDO 噪声详解

| VOUT(目标值) | R1 | R2 | 1+R1/R2 |

| 3.3V | 31.25k? | 10k? | 4.125 |

| 1.8V | 12.5k? | 10k? | 2.25 |

| 1.2V | 5k? | 10k? | 1.5 |

| 0.8V | 0?(短路OUT 节点至FB节点) | 开路 | 1 |

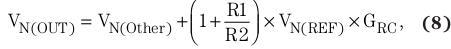

首先,使用一个可忽略不计的小 CNR,研究放大器增益的影响。图 6 显示了 RMS 噪声与输出电压设置的对比情况。如前所述,主要噪声源 VN(REF) 通过反馈电阻器 R1 和 R2 的比放大。我们将方程式 7 修改为方程式 8 的形式:

其中,VN(Other)为所有其它噪声源的和。

如果方程式 8 拟合y=ax + b的线性曲线,如图 6 中红色虚线所示,则 VN(REF)(斜率项)可估算为 19 µVRMS,而 VN(Other)(y 截距项)为 10.5 µVRMS。正如在后面我们根据"降噪(NR)引脚效应"说明的那样,CNR 的值为 1pF,目的是将 RC 滤波器效应最小化至可忽略不计水平,而 GRC 被看作等于 1。在这种情况下,基本假定 VN(REF) 为主要噪声源。

请注意,当 OUT 节点短路至 FB 节点时噪声最小,其让方程式 8 的放大器增益(1 + R1/R2)等于1(R1=0)。图 6 显示,该最小噪声点约为 30 µVRMS。

抵销放大参考噪声

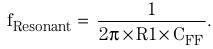

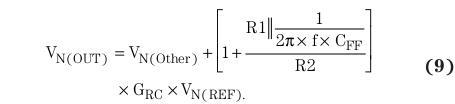

本小节介绍一种实现最小输出噪声配置的有效方法。如图 7 所示,一个前馈电容器 CFF 向前传送(绕开)R1 周围的输出噪声。这种绕开或者短路做法,可防止在高于 R1 和 CFF 谐振频率 fResonant 时参考噪声因误差放大器增益而增加,其中:

输出噪声变为:

图 7 使用噪声最小化前馈电容(CFF) 的 LDO 拓扑

图 8 显示了RMS噪声相对于前馈电容 (CFF) 和不同输出电压设置的变化。请注意,每个 RMS 图线上各点代表上述电路状态下整个给定带宽的完整噪声统计平均数。正如我们预计的那样,所有曲线朝 30 µVRMS 左右的最小输出噪声汇集;换句话说,由于 CFF 效应,噪声汇聚于 VN(REF) + VN(Other)。

图 8 前馈电容对噪声的影响

图 8 对此进行了描述。CFF 值大于 100nF时,方程式 8 中1 + R1/R2 的放大器增益被抵销掉。出现这种情况的原因是,尽管低频噪声未被 CFF 完全抵销,但是低频噪声对 RMS 计算的总统计平均数影响不大。为了观察 CFF 的实际效果,我们必需查看噪声电压的实际频谱密度图(图9)。图9表明,CFF=10µF 曲线的噪声最小,但是某些频率以上时所有曲线均接近于这条最小噪声曲线。这些频率相当于由 R1 和 CFF 值决定的谐振极点频率。R1 等于 31.6 k? 时计算得到的 CFF值,请参见表 2。

表 2 计算得谐振频率

|

| CFF=10pF | CFF=1nF | CFF=100nF | CFF=10µF |

| fResonant | 504kHz | 504kHz | 504kHz | 504kHz |

图 9 表明,50 Hz 附近时,CFF=100 nF 曲线转降。5 kHz 附近时,CFF=1 nF 曲线转降,但是 CFF=10 pF 时谐振频率受 LDO 噪声总内部效应影响。通过观察图 9,我们后面均假设 CFF=10µF 最小噪声。

图 9 各种 CFF 值的输出频谱噪声密度

降噪 (NR) 引脚的效果

在 NR 引脚和接地之间使用 RC 滤波器电容(CNR)时,GRC 下降。图 10 表明 RMS 噪声为 CNR 的函数(参见图 5)。稍后,我们将在第三段"其它技术考虑因素"中说明这两条曲线的差异。

图 10 RMS 噪声与降噪电容的关系

图 10 利用 10 Hz 到 100 kHz 更宽融合范围,来捕捉低频区域的性能差异。CNR=1pF 时,两条曲线表现出非常高的RMS噪声值。尽管图 10 没有显示,但不管是否 CNR=1pF,都没有 RMS 噪声差异。这就是为什么在前面小节"放大参考噪声"中,我们把GRC被看作等于 1 的原因。

正如我们预计的那样,随着 CNR 增加,RMS 噪声下降,并在 CNR=1µF 时朝约12.5 µVRMS 的最小输出噪声汇聚。

CFF= 10 µF 时,放大器增益(1 + R1/R2)可以忽略不计。因此,方程式 8 可以简写为:

正如我们看到的那样,VN(Other) 并不受 CNR 影响。因此,CNR 保持 10.5 µVRMS,其由图 6 所示数据曲线拟合度决定。方程式 10 可以表示为:

接下来,我们要确定 GRC 降噪电容的影响,这一点很重要。图 10 中曲线的最小测量噪声,让我们可以将方程式10改写为:

TPS7A8101 TPS74401 LDO 电源管理 德州仪器 相关文章:

- 如何设计一个合适的系统电源(上)(11-20)

- 如何将CMOS LDO应用于便携式产品中(01-15)

- 用低压差线性稳压器优化开关电源设计(01-18)

- LDO稳压器等效串联电阻的稳定范围(01-24)

- 低电压PLD/FPGA的供电设计(01-24)

- 拥有线性稳压器特性的下一代移动DC-to-DC转换器(02-08)