基于多端口串行Flash的条形LED显示屏控制

在LED 显示屏应用中,超长条形LED 屏是非常广泛的一种形式,其特点是长度"特别长"而宽度窄。 超长LED 显示屏目前没有明确的定义,可以将其水平方向的点数定义为≥2 048 比较合适。

以由1 /4 扫描P10 单元板( 点间距10 mm) 组成的超长条形LED 显示屏为例,当水平方向的点数为2 048 时,其水平方向物理尺寸为20. 48 m. LED 屏的宽度( 垂直方向) 点数一般为16、24 和32 点,最多不超过64 点,应用中以能够显示一行各类字体的汉字为主。 为保证刷新率,在对超长LED 显示屏的控制上,要求在规定时间内送出更多数据,普通的LED 显示屏控制卡很难实现控制要求。

本文在分析现有各种条形LED 显示屏单元板电路的基础上,提出了一种基于多端口串行Flash存储器的LED 显示控制系统。 利用单片机的SPI接口产生可控时钟,将多端口串行Flash 存储器中的显示数据以"DMA"方式直接输出至超长条形LED 显示屏。

1 常用单元板内部串行移位寄存器连接方式

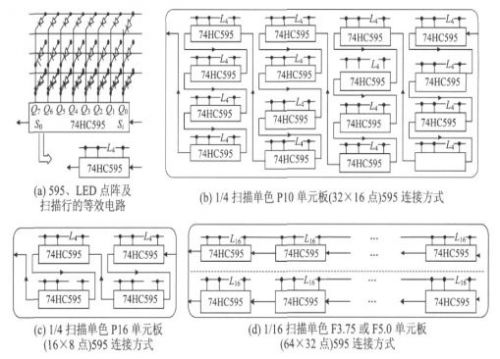

图1 为3 种常用单元板内部串行移位寄存器连接方式。 其中图1( a) 为单元板74HC595 与LED发光管点阵连接关系及简化表示电路。 LED 显示屏单元板内部使用的串行移位寄存器一般为74HC595、MBI5026 或MBI5026 兼容芯片,而MBI5026 可以看成是由两片74HC595 级联构成,为恒流源驱动模式,更适合LED 的驱动。

图1( b) 、( c) 、( d) 分别为P10、P16、F3. 75 或F5. 0单元板的连接方式。

图1 3 种常用单元板内部串行移位寄存器连接方式

2 超长LED 显示屏面临的问题及解决方案

目前,市场上大量的门头屏( 条形LED 显示屏) 是LED 显示屏应用最广的一种形式。 从技术上来说,门头屏的水平方向点数从256 点至数千点,而高度一般不超过64 点。 随着市场需求和显示精度的提高,数千点长度的超长LED 显示屏需求量在不断加大。 普通的LED 显示屏控制卡难于满足刷新率的要求,以在长度上像素点是4 096 的F3. 75 LED 显示屏为例,设刷新率为60 Hz,其SCK时钟周期至少为106 /60 /16 /4 096 = 0. 254 μs = 254 ns.

解决超长LED 显示屏数据输出的方法有两种: 一是选择高性能嵌入式处理器和FPGA 芯片,该方法控制卡成本较高; 二是巧妙应用单片机上的特殊功能部件并优化组织数据算法,这种方法成本很低。 本文采用的就是第2 种方法,通过优化算法将数据预先写入多端口串行Flash 存储器SST26VF016B 中,利用STC12C5616 单片机的SPI部件产生高速可控SCK 时钟,将多端口串行Flash存储器中的显示数据以"DMA"方式直接输出至超长条形LED 显示屏中,满足超长LED 显示屏的显示要求。

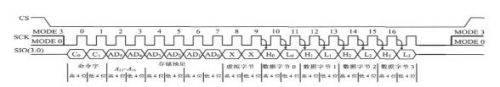

超长LED 显示屏高度一般不超过64 点,若控制1 /16 扫描单色LED 显示屏,SST26VF016B 存储器的4 位数据端口正好满足LED 显示屏数据口宽度的需要。 图2 为SST26VF016B 存储器的控制时序,CS 为SST26VF016B 存储器的片选端,所有对存储器的操作都要在CS 为低电平期间进行;SCK 为时钟线,当空闲模式时,SCK 信号可以处于低电平状态( MODE 0) ,也可以处在高电平状态( MODE 3) ; SIO( 3∶ 0) 为4 位数据端口,在数据传输时,先传字节的高4 位,再传字节的低4 位。 从存储器的控制时序可以看出,对存储器的控制按照命令字、24 位存储地址、虚拟字节、数据字节0 到数据字节N 的顺序发送。 存储器的命令字可以实现对存储器进行片擦除、扇区擦除、单字节读写、连续字节读写等功能,完全能够满足超长LED 显示屏对存储器的容量和控制方式的要求。

图2 SST26VF016B 存储器的控制时序。

STC12C5616 是STC 公司推出的高速1T 单片机,时钟频率可达30 MHz 以上,其内部集成一个高速串行通信接口部件( 即SPI 接口)。 当STC12C5616 的SPI 部件采用主模式工作时,其SPI时钟输出频率( fclk) 可以达到晶振频率( fosc) 的1 /4 倍,并且可以灵活配置它的时钟相位和时钟极性,既满足对SST26VF016B存储器控制的要求,又满足超长LED 显示屏对时钟的要求。

3 超长LED 显示屏控制卡电路设计

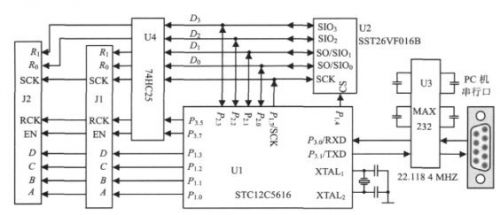

利用串行Flash 存储器SST26VF016B 的多位数据口存储器和STC12C5616 单片机的SPI 部件能产生高速SCK 时钟的特点,将显示数据从串行Flash存储器旁路输出至LED 显示屏,电路如图3 所示。

图3 超长LED 显示屏控制卡电路图。

当显示屏的动态刷新速率达到50 次/s 时,在1 /16 扫描的LED 显示屏上,一行显示时间要小于1 /50 /16 s,即1. 25 ms. 在控制卡设计上,当fosc =22 MHz时,串行Flash 时钟频率fclk = 1 /4 fosc =5. 5 MHz,故4 096 个CLK 时钟所需时间为4 096 ×

- 低压闪光灯方案(06-23)

- flash接口电路的实现(07-18)

- 一种支持ISP的Flash在嵌入式设计中的应用(08-19)

- 提高MSP430G 系列单片机的Flash 擦写寿命方法(08-28)

- 基于FLASH介质嵌入式存储方案的设计与实现(04-20)

- 基于虚拟通道的Flash映射技术(01-20)