使用采样保持技术实现运算放大器建立时间测定

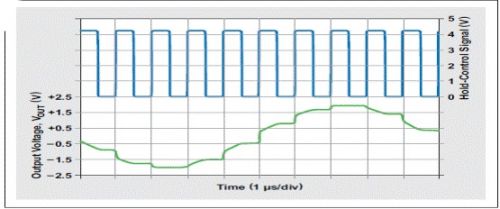

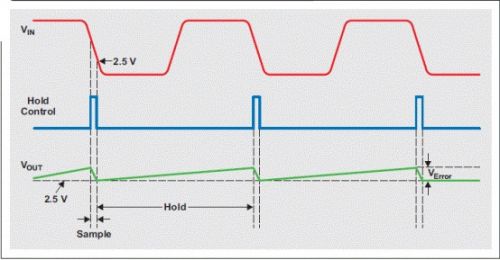

图4描述了如何使用一个S/H电路捕获曲线上的各个点,而该S/H电路将标记用作保持控制信号。设计人员可以通过移动标记位置来捕获曲线上的连续各点。在记录完所有点以后,可将S/H曲线绘制出来进行分析。使用MATLAB®或者LabVIEW™等软件对波形生成器编程,以此来改变标记和记录结果,是一种非常简单的方法。将标记设定在位置1后,S/H电路追踪标记为高时的VIN电压电平,并在标记为低时保持该值。在位置1处,输出保持在1V。在位置2处,输出保持在0.2V。

图 4 AWG610输出的标记同步例子

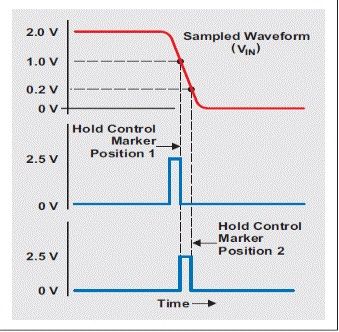

图5显示了建立时间测量的测试装置,其使用AWG610和OPA615实现S/H功能。所有信号线路均为50Ω。波形生成器输出用作测试信号,并使用两个S/H电路:一个测量受测器件(OPA656)的输入,另一个测量受测器件的输出。数字万用表(DMM)用于记录各个保持值。

图 5 建立时间测量测试装置

例如,我们对100 ns的建立时间进行测量。假设波形生成器经过了编程,目的是不断输出50%占空比的方波,持续时间为200ns。标记最初被设定在波形生成器输出的降沿开端处。生成器持续工作(执行许多个采样和保持周期),而S/H电路对其输出电压求积分,以获得一个稳定的DC值。之后,由DMM记录该值,然后测试工程师将标记移至下一个位置,重复前面的周期,直到记录完100 ns的数据为止。

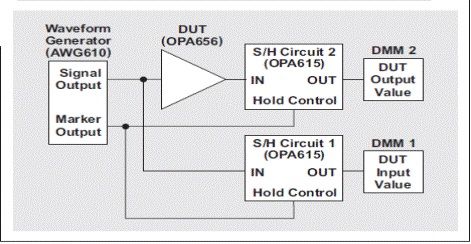

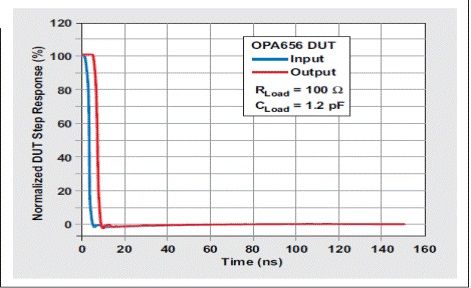

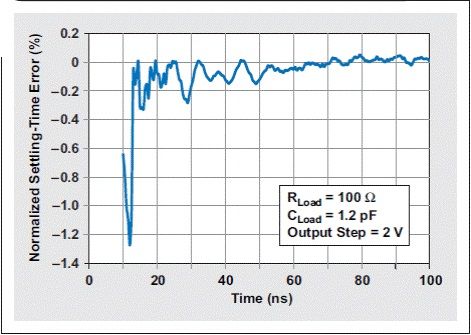

图6显示了使用图5所示测试装置所得结果的波形图。为了获得建立时间误差波形,对DC误差进行补偿,并对输出进行输入标准化。图7显示了所得结果。

图 6 运算放大器输入和输出阶跃波形

局限性与挑战

需要时刻谨记的是,这里介绍的测试装置存在一些局限性。如果有疑问,设计人员应始终使用下列方程式:

I = CHOLD × dv/dt

使用该方程式时,应根据下列3个因素选择初始CHOLD的大小:

1、保持期间,OTA偏置电流会流入或者流出电容器,从而影响保持电压的准确性。

2、由于电容器会因偏置电流而出现压降,应根据测量应达到的误差百分比选择三角接线电压。

3、增量时间为采样电压保持的时间,不能长于要测量的计划建立时间。

例如,下列条件下CHOLD不能小于50 pF:OTA偏置电流为0.5 µA;欲达到1-VPP信号0.1%以下的误差;要测量的时长为100 ns。

其他考虑因素

采样时间的长短会极大影响测量结果。保持期间,采样电容器电压始终会偏离于预计DC值,因为OTA要求偏置电流。之后,电压被再调节回到采样期间的预计DC值。因此,读取S/H电路输出的DMM必需使用这种三角波形的平均值。图8描述了这种现象。要想减小这种误差,需最小化保持时间,并最大化电容器尺寸。记住,采样电容器越大,充电电荷积分获得稳定DC值所需的S/H周期(积分时间)也就越多。

图 7 运算放大器标准化稳定误差

图 8 采样电容器的充电漏泄

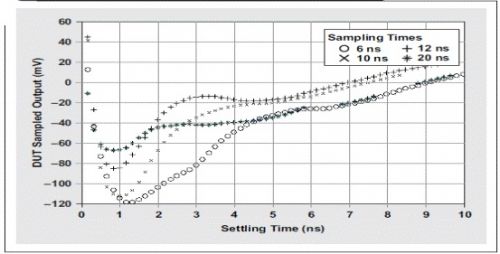

当然,增加采样时间并不能缓解漏电问题。应使用最小采样时间,以保证SOTA保持时间延迟,并确保追踪S/H电路输入的同时有足够的时间采样电容器的充电/放电。图9显示了相同保持和积分时间使用不同采样时间时,所记录的运算放大器建立时间。这些结果均根据一个6GHz、10比特示波器的相同波形测量得到,其显示最大过冲为-60mV。使用20ns采样时间的测量结果与该示波器显示情况相匹配,但需对结果使用大滤波。相反,使用6ns的测量仅使用了小滤波,但产生了更大的过冲,其为测量中产生的人为现象。

图 9 不同采样时间测量得建立时间

结论

测量建立时间的方法有很多。本文为您介绍了一种简单但却准确的测量方法,它使用一个相对快速的波形生成器和一个S/H电路。了解这种方法存在的局限性以后,使用者便能够对所有测量参数进行必要的调整,从而获得给定时间范围和预计准确度的最佳结果。

立即加入德州仪器技术社区

- 一种用于高速ADC的采样保持电源电路的设计(10-21)

- Giga ADC 介绍及杂散分析(上)(01-22)

- 一种用于13 bit 40 MS/s流水线ADC中的采样保持电路设计(03-30)

- 适用于12 bit流水线ADC采样保持电路的设计(01-17)

- 采样保持电路中全差分运算放大器的设计与仿真(11-09)

- 一个用于流水线模数转换器的高精度、低功耗采样保(07-30)