驱动集成电路功率级中瞬态问题的处理

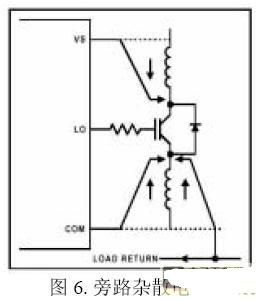

减小驱动IC杂数电感:

2a、如图6所示连接VS和COM;

2b、使用 短的直接连线减小门极电路杂散电感;

2c、驱动IC距离功率器件越近越好。

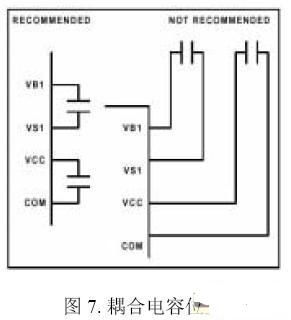

改善耦合

3a、提高自举电容(Cb)值,至少使用一个低ESR电容,减小由于VS负

过冲而产生的过充电。

3b、在VCC和COM间使用第二个低ESR电容,这个电容为低端输出缓冲

电路和自举电路再充电推供电源,

建议该值至少是Cb的十倍。

3c、尽量将去耦电容靠近相应的管脚,如图7。

3d、如果需要在自举 二极管中串联电阻,要确保VB不会降到COM以下,

特别是在启动时和极端频率和占空比下。

适当的利用上述推荐方法,可以从根本最小化VS负过冲的影响,如果负过冲水平仍然很高,就应考虑减小dv/dt了。

也许可以用外部吸收电路或增加栅极驱动电阻来折衰效率和开关速率。如果系统不能允许,应适当考虑快速反并联嵌位二极管,HEXFRED是理想的选择。

8.提升VS负过冲免疫力

在最坏条件下,如果主要信号在确定的极限值内,就不再需要采取措施。然而,在噪声非常大的环境中,采用上面措施,VS负过冲仍然超过,就需要进一步提高驱动IC的容错能力。我们推荐两种不同方法来改善负过冲免疫力。

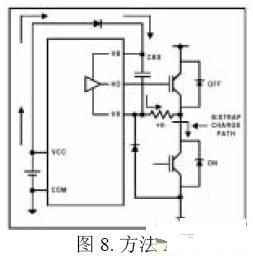

方法A:

在VS脚到桥电路中点串联电阻,限制当负过冲时流入VS脚的电流。当电阻为或更低时是可以的。

既然自举电容充电经过此电阻,如图8,如果此电阻值过大,可能在启动时引起直通发生。如果有栅极电阻,栅极电阻应减小,以保证高端和低端栅极电阻相等。

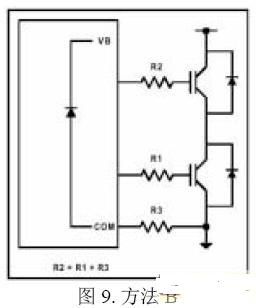

方法B:

另外一个方法是:在COM和低端器件源极或发射极加入一个电阻,如图9,而自举电容充电不经过此电阻,这种方法较灵活,可选择较大的电阻并提供很好的保护。

这个电阻可限制流入600V二极管D2的电流(图3),同样,驱动的对称性要求高低端栅极电阻相等,所以低端栅极电阻应适应减小以满足要求。

注意:

& nbsp;

当使用的驱动IC没有分开的逻辑地时,例如有些IC的输入和输出共享一个地COM,上述讨论的两种方法都可以应用,然而应注意并确保输入逻辑在允许电平内。

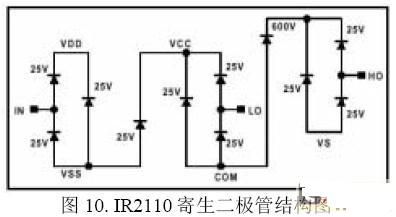

9.附录1 : IR2110寄生二极管结构

图10是IR2110的寄生二极管结构图,这基本体现了绝对最大额定值表。IR2110有独立逻辑地和输出地,在某些驱动IC中,由于管脚的限制,这两个地合并为一个。

- 基于新型ASSP LTC3455的硬盘MP3电源设计(06-07)

- 单片彩色LCoS显示系统的设计实现(09-09)

- 具有开关电源通路管理的下一代电源管理集成电路(08-28)

- 如何利用DCP获得更精确的性能(10-01)

- 集成电路的种类与用途(09-20)

- CMOS集成电路中ESD保护技术研究(10-17)