基于MSI的N进制计数器设计方法研究

1绪论

计数器是数字逻辑系统中的基本部件,它是数字系统中用得最多的时序逻辑电路,其主要功能就是用计数器的不同状态来记忆输入脉冲的个数。除此以外还具有定时、分频、运算等逻辑功能。计数器不仅能用于对时钟脉冲的计数,还可使用于定时、分频、产生节拍脉冲以及进行数字运算等。只要是稍微复杂一些的

数字系统,几乎没有不包含计数器的。通常把满足N=2n的计数器称为二进制规则计数器,有些数字定时、分频系统中,常需要N≠2n的任意进制计数器。

当我们在设计任意进制计数器(即计数模不是2及10)时,一般采用现有的中规模集成电路(MediumScaleIntegratiON,MSI)芯片,通过适当的反馈连接加以实现。而市场上现成的中规模集成电路芯片常见的只有十进制计数器和十六进制计数器,而在实际应用中,如数字钟电路中,却需要二十四进制和六十进制计数器,因此要将现有计数器改造成任意进制计数器。利用MSI芯片进行适当的连接就可以构成任意进制计数,所使用的方法主要有反馈置零法、反馈预置法和级联法。

采用中规模集成计数器来设计任意进制计数器,使设计和调试工作更趋于简单,并且具有体积小,功耗低,可靠性高等优点。本文主要阐述了用中规模集成计数器设计任意进制同步加法计数器的设计思想,并对设计方法和步骤作了讨论。

2.MSI中规模计数器概述

2.1MSI中规模计数器芯片种类

MSI中规模计数器芯片有非常多的种类。若按触发时钟的方式分类有:同步计数器、异步计数器;若按进制的"模"分类有:二进制计数器、十进制计数器;若按计数的方式分类:有加法计数器、减法计数器和可逆(加/减)计数器;若按芯片的型号分类就更多了,如:仅74系列的4位二进制计数器芯片就有161、163、191、193、197等,十进制计数器芯片有160、162等。

2.2MSI中规模计数器工作原理

2.2.1.以十进制同步计数器74LS160为例

74LS160的功能

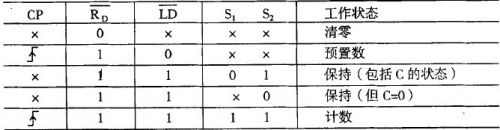

表174LS160功能表

根据功能表,74LSl60的功能说明如下:

(1)异步清零功能。当CR=0时,不论其他输入如何,输出Q3Q2Q1Q0为0000,表中"×"表示任意。

(2)同步并行置数功能。LD为预置数控制端,在CR=1的条件下,LD=0时,在CP上升沿的作用下,预置好的数据d3d2dld0被并行地送到输出端,即此时的Q3Q2Q1Q0为d3d2dld0。

(3)保持功能。在CR=1和LD=1的前提下,只要TTTP=0,则计数器不工作,输出保持原状态不变。

(4)计数功能。正常计数时,必须使CR=1,LD=1,TTTP=1,此时在CP的上升沿的作用下,计

数器对CP的个数进行加法计数。当计数到输出Q3Q2Q1Q0为1001时,C0=1,C0=1的维持时间是从Q3Q2QlQ0为1001时起到QaQ2Q1Q0状态变化时止。

2.2.2以四位二进制计数器为例

74LS161功能

表274LS161功能表

从功能表(一)可以看到,74LS161处于计数状态时,引出端RD,LD,S:,S:都应为"1"(接高电平)。如果取其中一片T4161作为低位计数器〔记作(1)〕,对该片计数器来讲,每来一个CP就计一次数,它始终工作在计数状态。

3.设计方案

3.1采用反馈置零法来设计任意进制计数器

对于74LS160属于异步置零输入端的计数器,它是当置零输入端出现有效电平(低电平)后计数器立即被置零,不受时钟信号的控制。而对于74LS162/74LS163属于同步置零输入端的计数器。它是当置零输入端出现有效电平(低电平)后计数器并不会立即被置零,必须等下一个时钟信号到达后,才能将计数器置零。两者用时必须加以区分。

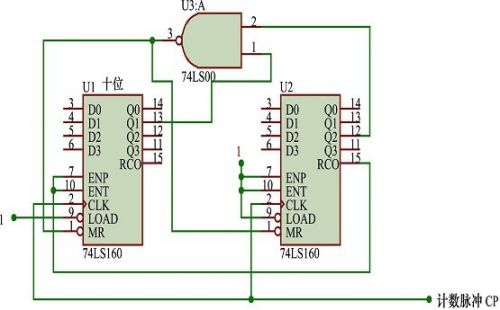

3.1.1采用并行法来设计24进制计数器

用74LS160并行置零法设计24进制计数器的电路图如图1所示。此电路的工作原理:先假设两芯片的置零输入端为1,则个位芯片由于计数控制端ENP=ENT=1,故该芯片始终处于计数状态;而十位芯片的ENP、ENT连接的是个位芯片的进位控制端RCO,只有当个位芯片的计数状态Q3Q2Q1Q0为1001时,RCO才为1.十位芯片才能计数。如果没有反馈置零(即MR端恒接高电平)则电路是一个100进制计数器。现在电路中加上了反馈,当计数状态(00100100)8421BCD码=(24)10时,与非门输出为零。由于74LS160属于异步置零,且复位控制端MR低电平有效,所以计数器立即置零。由于电路中的状态(24)10转瞬即逝,显示不出。故电路的有效状态从(00)10到(23)10共24个,故此电路为24进制计数器。

图1用74LS160并行置零法设计24进制计数器

另外如果采用同步置零74LS162计数器来设计24进制计数器,那么反馈代码必须是(23)10相应的8421BCD码为00100011.由此可见反馈信号应取自十位芯片的Q1及个位芯片的Q1和Q0,相应的与非门应改成四输入端与非门。用74LS162并行置零法设计

- 基于门控时钟的低功耗时序电路设计(07-13)

- N进制异步计数器设计方案(12-06)

- 具有数据记录功能的无线温度监控系统(06-05)

- 基于CC4060的环境湿度测试仪的设计与实现(07-16)

- 一种简单的二进制/BCD转换电路(07-11)

- 介绍模拟开关的电路及工作原理(07-23)