多个AD9779 TxDAC器件的同步

简介

AD9779 TxDAC的DAC输出采样速率最高可达1 GSPS.在某些应用中,例如需要波束导引的应用,用户可以同步多个AD9779.因此,当AD9779以接近最高速度工作时,TxDAC时序特性变得至关重要。

本应用笔记不讨论AD9779运作涉及到的全部细节。若要全面了解其内部数字引擎,用户应参阅AD9779数据手册。本应用笔记扩展了SYNC_I的使用,使多个AD9779器件实现相同的REFCLK/DATACLK同步。

在传统的插值TxDAC中,当DAC采用DAC输出采样速率时钟驱动时,会产生两个问题。第一,可能难以确定输入数据在哪一个DACCLK沿锁存。多数DAC解决这一问题的方法是提供一个DATACLK信号输出,以指示输入寄存器锁存沿的位置。第二个问题发生于用户试图同步多个TxDAC时,这是本应用笔记的主题。多个器件的DATACLK输出并不保证同步,上电时仅靠器件本身不大可能实现同步。AD9779解决这一问题的方法是为数据同步提供第二个时钟,该时钟称为SYNC_I,是AD9779的一路输入,可以用来同步多个AD9779的输入数据锁存。

本应用笔记将详细说明用于同步多个AD9779器件的数字数据输入的方法。DAC输出的相位对齐通过设计保证,精度小于一个DACCLK输出周期。然而,由于输出延迟不匹配(室温下及冷热温度下),多个DAC输出的相位对齐可能存在细微的不一致,本应用笔记不讨论这一问题。

同步方案

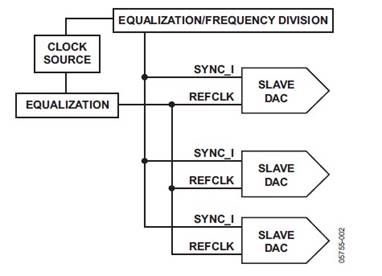

同步多个AD9779 DAC有两种方案。在第一种方案中,一个器件用作主器件,其余器件用作从器件。在第二种方案中,所有器件都是从器件。两种方案具有相同的时序限制,不存在性能权衡。主/从模式和从模式的框图分别如图1和图2所示。

图1. 主/从SYNC_I/O分配

图2. 从SYNC_I分配

同步详解

工作中,差分时钟信号驱动所有主器件和从器件的AD9779 REFCLK输入。REFCLK输入接收器是一个高增益差分放大器,各差分输入需要接近400 mV的共模输入电平和至少400 mV p-p的摆幅。

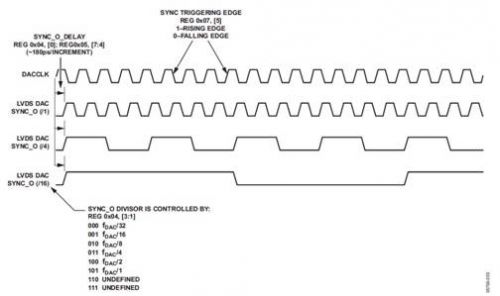

如果选定了主器件,可以使能主器件的差分LVDS输出信号,该信号称为SYNC_O+和SYNC_O?.通过寄存器0x07的位5,可以将SYNC_O设置为在DACCLK的上升沿或下降沿触发。SYNC_O还有一个可编程的延迟,可以通过寄存器0x04的位0 (MSB)和寄存器0x05的位[7:4] (LSB)设置。SYNC_O通过将同步驱动器使能位(寄存器0x07的位6)置1而使能。SYNC_O信号速度可以是REFCLK速度的整数除数,通过寄存器0x04的位[3:1]设置。主器件的REFCLK输入和SYNC_O信号的可能时序情况如图3所示。

图3. DACCLK SYNC_O时序

SYNC_O驱动器和SYNC_I接收器规定用于LVDS电平(参见AD9779数据手册)。

驱动多个AD9779器件的CMOS数字数据输入的并行数字输入总线在时间上应均衡。如果多条数据总线不均衡,可以利用AD9779的编程能力,通过DATA_CLOCK_DELAY(寄存器0x04的位[7:4])以大约180 ps的增量偏移各AD9779的锁存时间。AD9779无法补偿单条数据总线中包含的位偏斜。

在所有AD9779器件上,SYNC_I、REFCLK输入与CMOS数字输入数据之间都存在建立保持关系。AD9779数据手册的"时序信息"部分说明了这些时序关系。

SYNC_O和SYNC_O_DELAY的推荐应用是利用SYNC_O_DELAY来均衡SYNC_I和REFCLK的时序,确保其时序关系有效。

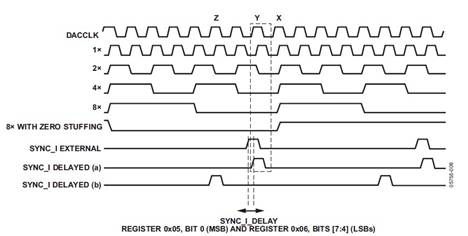

SYNC_I具有其自己的可编程延迟,可以通过寄存器0x05的位0 (MSB)和寄存器0x06的位[7:4] (LSB)设置。SYNC_I_DELAY可以用于均衡不理想或者选用图2所示电路的应用中。SYNC_I通过将同步接收器使能位(寄存器0x07的位7)置1而使能。

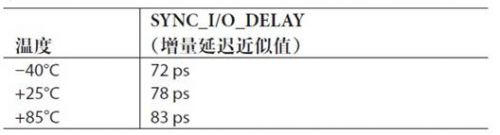

表1显示了增量延迟SYNC_O_DELAY和SYNC_I_DELAY,这些延迟可以通过SPI寄存器设置。

表 1

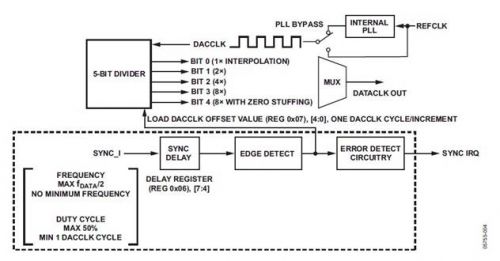

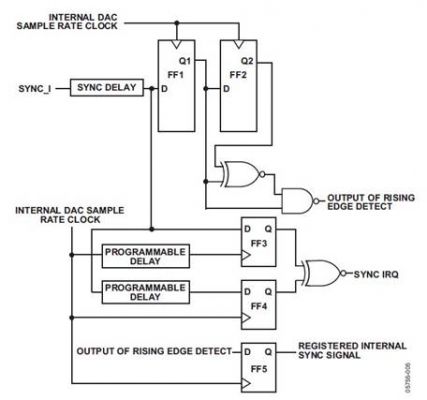

图4所示为用于同步多个AD9779的内部电路框图。在可编程的延迟后,SYNC_I信号得到处理,使得对于SYNC_I的每个上升沿,只剩下一个长度为DACCLK周期的脉冲。注意在这种情况下,DACCLK代表AD9779 DAC的内部采样速率时钟,它可以与REFCLK相同,具体取决于对AD9779的编程。长度为DACCLK周期的该单一脉冲驱动图4中的5位分频器的负载信号。分频器延迟逻辑的5信号输出代表所有插值速率的可能DATACLK信号,包括使能零填充的可能性。通过设置DACCLK偏移寄存器,图4中的位1至位4可以DACCLK周期为增量进行延迟。5位分频器的内部时序、负载信号的影响和DACCLK偏移值如图6所示。

图4. AD9779多DAC同步电路框图

边沿检测器还驱动误差检测电路,图5更详细地显示了该电路。可编程误差检测电路可以用来测量时序裕量,如果超出时序裕量,将产生中断。

图5. 可编程时序裕量和负载信号产生详情

图6. SYNC_I、DACCLK和DATACLK的内部时序

图5更详细地显示了图4中虚线所示的电路。在电路内部,FF5输入端的信

- 如何收敛高速ADC电路(08-28)

- 基于MSC1201的温度控制系统设计(07-30)

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- 如何使低功耗放大器在便携式产品中提高性能(10-03)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 高速DAC AD9712B/AD9713B的原理和应用(11-30)