低噪声、高线性度的3.5GHz LNA设计

主要是对f0周围的频率范围感兴趣。值得注意的是,制造商提供的许多s2p文件也是频率受限的。

电感模型使用了最接近f0的频率点(通常是1.7GHz或1.8GHz,具体取决于制造商,这在数据手册中可以找到)规定的QUL典型值,然后可以使用Q∝√f关系外推到3.5GHz以上。电感的寄生电容(Cpst)从公布的SRF典型值计算得到,但需要增加额外的0.1pF,以代表与PCB焊盘有关的寄生电容。电容模型中的寄生电感(Lpst)遵循供应商软件中提供的值。

结果与讨论

原型在以下条件下进行评估:5V供电电压,3.5GHz中心频率和室温。通过使用3.3kΩ的RBIAS值将器件电流Idd设置为60±5mA。

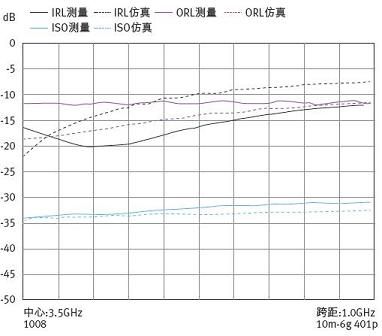

最首要的设计目标是同时达到良好的反射损耗(IRL<-15dB)和低噪声水平(F<1dB)。这个要求最初来自双工器或滤波器对端接敏感的基站(BTS)市场部分。较老的基站实现通常依赖位于平衡LNA输入端的隔离器或积分耦合器同时实现低反射损耗和噪声系数。但是,鉴于成本和空间的考虑,较新的实现设法取消了隔离器或积分耦合器。在图5中,在3.5GHz处测得的性能是:IRL=-16dB,ORL=-12dB和ISO=-32dB。在约300MHz处产生的最小反射损耗低于目标要求,然而并不需要重新调谐输入匹配电路,因为其它要求已经满足。除此之外,还需要有比普通E12更高粒度的LC值,将中频带搬移到准确的3.5GHz。测量得到的ISO要比同样尺寸的单个EPHEMT好13dB左右。

图5:测量和仿真得到的输入反射损耗(IRL)、输出反射损耗(ORL)和反向隔离(ISO)与频率的关系。

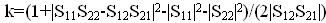

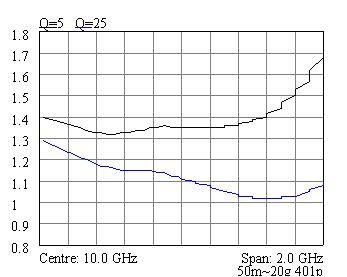

在3.5GHz测得的噪声系数稍低于1dB。由于前述的输入匹配误差,最小值被偏移到3GHz。最小的F要比单个PHEMT参考约低0.1dB。最大增益17.6dB发生在2.6GHz,但保持了15.6dB的足够增益。

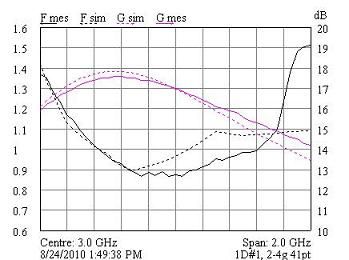

对最终的LNA潜在的不稳定性进行了彻底研究,结果见图6所示的图形。在通带之外,增益单调地下降,其较小的拐点位于14GHz和18GHz。造成峰值的可能原因是元件谐振和输入输出耦合,但当这些峰值低于单位增益时,在尺寸不合适的金属外壳中空腔共振风险很小。从图7还可以看出Rollett稳定系数(公式31),稳定性指标D=|S11S22-S12S21|。这两个指标都是根据测量到的板级s2p计算出来的。由于测量表明在整个评估的频率范围内k>1和D<1,因此,能够保证带正实数部分的任何端接都具有绝对稳定性。

图6:测量和仿真得到的噪声系数(F)和增益(G)与频率的关系。

图7:测量和仿真得到的增益(G)、Rollett稳定系数(k)和稳定性指标(D)与频率的关系。

由于接收机元件具有非线性,相邻通道信号可能形成三阶互调失真(IMD3)。由2f1-f2或2f2-f1关系确定的非线性不可能被滤除,因为它们非常接近有用信号。线性度的一个关键指标三阶交点OIP3被定义为基频信号功率(Pfund)和IMD3功率理论上的交叉点。在线性区域,OIP3可以利用公式3从IMD3幅度计算得到:

(公式3)

(公式3)

其中,ΔIM是基频信号功率和互调产物功率之间的差值(单位dB)。

评估这个设计时使用了位于3500MHz和3501MHz的两个输入声调。然而,不希望有其它频率间距去明显改变结果。如图8所示,在由Pi<-4dBm包围的线性工作区域内,OIP3≥35dBm。这要比单个PHEMT低1dB,这个值非常显著,因为VDS在共源共栅拓扑中只有一半。IMD中的零点或最佳点位于-6dBm输入驱动点,表明这是AB类操作。形成零点的原因是小信号IMD和大信号IMD在饱和开始时处于异相状态。

图8:测量得到的输出功率(Po)、三阶互调功率(IMD3)和三阶交点(OIP3)与频率的关系。

通过降低G和增加F使接收机减敏的阻塞现象可以由异步干扰源(如共享同一铁塔的强大的发射机)或同步源(如经过同时具有收发功能的收发器中的循环器或双工器泄漏的信号传输)造成。因此,具有高增益抑制阈值的元件可以更加有效地抵抗阻塞。增益抑制主要是由放大器中的非线性转移特性造成的,随着作为次要因素的散热渐增,放大器将被驱动到线性范围之外。

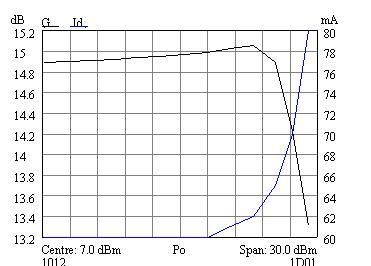

图9显示了+19dBm的输出1dB压缩点(P1dB),其类似于参考的单个EPHEMT。尽管共源共栅拓扑结构具有更低的VDS,还是获得了很高的P1dB,因为GaAs更低的体积电导率具有更少的热量损失,以及ePHEMT低膝点电压(0.3V)在钳位之前允许更大的电压摆幅。允许电流Id像AB类功放那样与功率的平方成正比(即Id∝Po2),也导致了更高的P1dB,在类似的设计中显示了在2.4GHz处有4dB的改善。

图9:测量到的G和Id与输出功率(Po)的关系。

本文小结

至此,已经用低成本、QFN2x2封装的MMIC成功设计出了具有优良噪声系数、增益和线性性能的3.5GHz LNA。结合芯片级的偏置调节器、ESD保护和稳定性网络,可以将外部元件数量

- 利用GaAs PHEMT设计MMIC LNA(11-15)

- 利用GaAsPHEMT设计MMICLNA(12-30)

- DC~40 GHz反射型GaAs MMIC SPST开关(04-20)

- SiC衬底X波段GaN MMIC的研究(04-16)

- CMOS低噪声放大器中的输入匹配研究与设计(08-19)

- 利用阻性负载增强LNA稳定性(中)(11-19)